## Asymmetric Runtime Environments for Increased-Performance Speculative PDES

Dipartimento di Ingegneria Informatica Automatica e Gestionale "Antonio Ruberti"

Master of Science in Engineering in Computer Science

Candidate Lorenzo Altamura ID number 1538468

Thesis Advisor Prof. Alessandro Pellegrini Co-Advisor Prof. Bruno Ciciani

Academic Year 2018/2019

Thesis defended on 20 January 2020 in front of a Board of Examiners composed by:

Prof. Riccardo Rosati (chairman)

Prof. Aris Anagnostopoulos

Prof. Riccardo Lazzeretti

Prof. Alessandro Pellegrini

Prof. Leonardo Querzoni

Asymmetric Runtime Environments for Increased-Performance Speculative PDES Master's thesis. Sapienza – University of Rome

© 2020 Lorenzo Altamura. All rights reserved

This thesis has been typeset by LATEX and the Sapthesis class.

Version: January 15, 2020

Author's email: altamura.1538468@studenti.uniroma1.it

# Acknowledgements

I would like to thank Prof. Alessandro Pellegrini for providing me with all the support I needed throughout all these months in which I've learned so much. I would also like to thank Prof. Bruno Ciciani for the precious advice and Dr. Stefano Conoci for the help offered during the initial phases of this work.

My deepest gratitude goes to everyone who supported me along this journey, to my parents, sister and grandmother and to my dearest friends Jonattan and Matteo. A special recognition is addressed to my colleagues at DIAG who shared the path with me, especially to Roberto Adduci, Roberto Avagliano, Paolo Mastrobuono Battisti, Domenico Ciampa, Luca Deodati, Andrea Fantoli, Moreno Labbate, Chiara Mele, Marzio Monticelli, Riccardo Ostani and Riccardo Vecchi.

# Abstract

Future exascale systems will require runtime environments able to manage the complexity of the underlying heterogeneus hardware. This thesis discusses about asymmetric features in existing high performance applications to obtain consistent increase in terms of performance by properly exploiting the asymmetry shown by current pre-exascale systems. In particular, the focus is on parallel discrete events simulation (PDES) and possible solutions to best exploit asymmetry in threads by limiting the drawbacks in terms of the overhead brought by the time warp optimistic synchronization protocol.

Experimental data show how relevant the gain in terms of performance is when self-adjusting algorithms autonomically manage the balance between asymmetric thread incarnations.

# Contents

| Introduction and Context |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| 1.1                      | Discrete-event simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

| 1.2                      | el discrete-event simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                                                                                                                                                                                                                                                                                                              |                                                  |  |  |

|                          | 1.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Introducing PDES                                                                                                                                                                                                                                                                                                                                                | 12                                               |  |  |

|                          | 1.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Implementation of synchronization                                                                                                                                                                                                                                                                                                                               | 14                                               |  |  |

|                          | 1.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The synchronization problem: stragglers                                                                                                                                                                                                                                                                                                                         | 16                                               |  |  |

|                          | 1.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The local causality constraint                                                                                                                                                                                                                                                                                                                                  | 16                                               |  |  |

|                          | 1.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Conservative and optimistic synchronization                                                                                                                                                                                                                                                                                                                     | 17                                               |  |  |

| 1.3                      | Optim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | istic Synchronization                                                                                                                                                                                                                                                                                                                                           | 19                                               |  |  |

|                          | 1.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Time warp                                                                                                                                                                                                                                                                                                                                                       | 20                                               |  |  |

|                          | 1.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Performance of optimistic synchronization                                                                                                                                                                                                                                                                                                                       | 22                                               |  |  |

|                          | 1.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Asymmetry in time warp                                                                                                                                                                                                                                                                                                                                          | 23                                               |  |  |

|                          | 1.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The choice of asymmetry                                                                                                                                                                                                                                                                                                                                         | 25                                               |  |  |

| Rela                     | ated Work 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

| Asy                      | Asymmetric Time Warp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

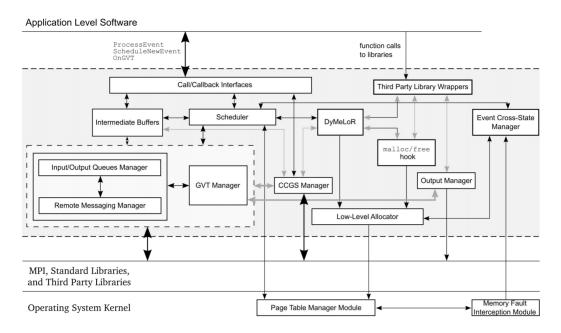

| 3.1                      | Asymmetric time warp architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

|                          | 3.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ensuring consistency                                                                                                                                                                                                                                                                                                                                            | 32                                               |  |  |

|                          | 3.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Checkpointing                                                                                                                                                                                                                                                                                                                                                   | 37                                               |  |  |

|                          | 3.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dynamic resources assignation                                                                                                                                                                                                                                                                                                                                   | 37                                               |  |  |

|                          | 3.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A comparison with classic symmetric multithread architecture                                                                                                                                                                                                                                                                                                    | 37                                               |  |  |

| 3.2                      | Dynamic thread role assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                 |                                                  |  |  |

|                          | 3.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | How to dynamically assign threads                                                                                                                                                                                                                                                                                                                               | 39                                               |  |  |

|                          | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>Relation of the second second</li></ol> | <ul> <li>1.1 Discret</li> <li>1.2 Paralle</li> <li>1.2.1</li> <li>1.2.2</li> <li>1.2.3</li> <li>1.2.4</li> <li>1.2.5</li> <li>1.3 Optime</li> <li>1.3.1</li> <li>1.3.2</li> <li>1.3.3</li> <li>1.3.4</li> <li>Related Works</li> <li>Asymmetri</li> <li>3.1</li> <li>3.1.1</li> <li>3.1.2</li> <li>3.1.3</li> <li>3.1.4</li> <li>3.2</li> <li>Dynari</li> </ul> | <ul> <li>1.1 Discrete-event simulation</li></ul> |  |  |

4

Asymmetric Runtime Environments for Increased-Performance Speculative PDES

| 4 | tal Assessment | 42                            |                                                                 |    |

|---|----------------|-------------------------------|-----------------------------------------------------------------|----|

|   | 4.1            | The ROme OpTimistic Simulator |                                                                 |    |

|   | 4.2            | Parameters                    |                                                                 |    |

|   | 4.3            | Measurements                  |                                                                 |    |

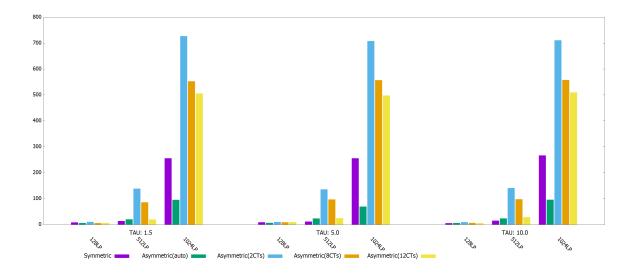

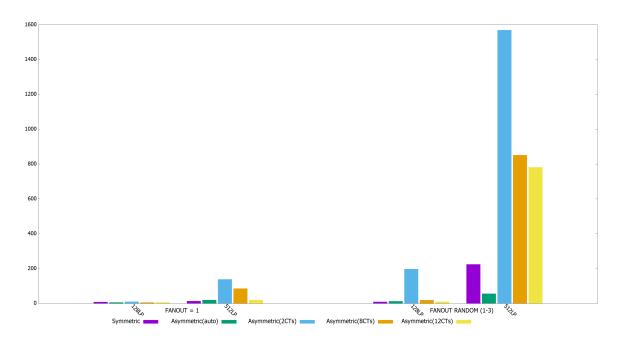

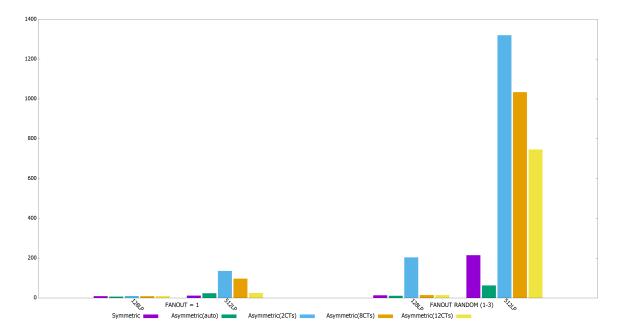

|   |                | 4.3.1                         | First test pool: fixed loop duration, fanout and random LP      |    |

|   |                |                               | event receiver                                                  | 45 |

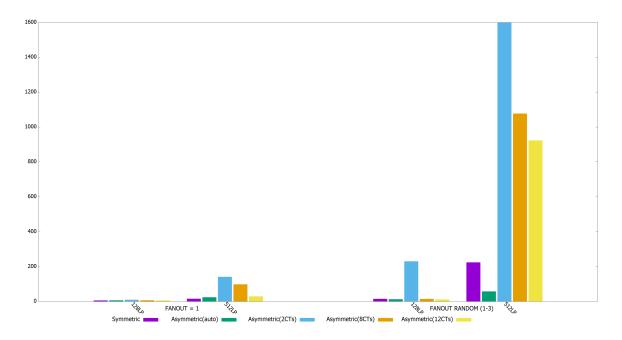

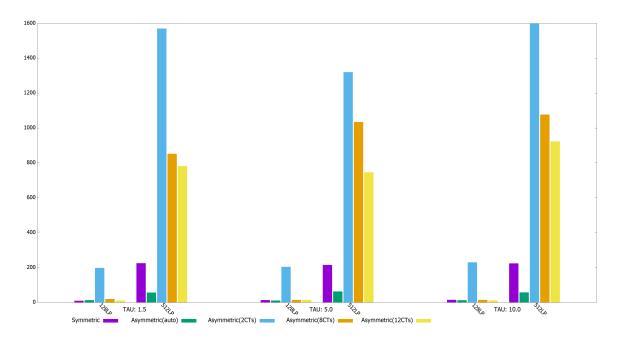

|   |                | 4.3.2                         | Second test pool: fixed loop duration, TAU and random LP        |    |

|   |                |                               | event receiver                                                  | 47 |

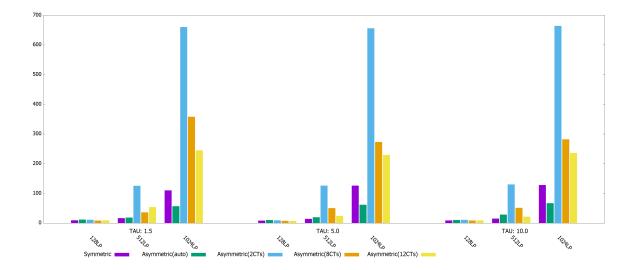

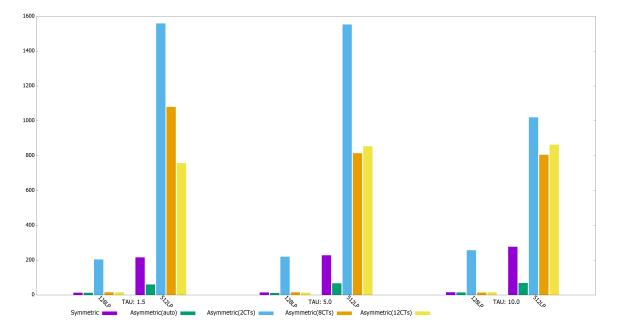

|   |                | 4.3.3                         | Third test pool: fixed loop duration, fanout and close LP event |    |

|   |                |                               | receiver                                                        | 49 |

| _ | 6              |                               |                                                                 | 51 |

| 5 | 5 Conclusions  |                               |                                                                 |    |

## Chapter 1

# **Introduction and Context**

In applied sciences, "simulation" plays a very important role as it is used as a mathematical, logical or scientific representation of any form of real phenomenon, may it be a system, an entity or a process. In cases where it is impossible or not convenient to reproduce in laboratory the real conditions implied in the study, simulation builds upon mathematical rules a reproduction of the case study, with dynamics and mechanics modeled as close as possible to the real system: the closer to reality the simulation is, the more reliable the analysis on behaviors will be. Comprehension of case studies is easier this way, as it implies less costs and a virtually unlimited amount of data to analyze. Anyway, this approach incurs some unavoidable approximations and assumptions that sometimes affect the validity of the outcomes.

In recent times, the use of computers widely spread into these practices, bringing an outstanding amount of benefits: for example, mathematical models were once used to solve the problem by finding analytical solutions predicting the behavior of the system by manipulating variables into extremely complex equations; computers helped to realize models with a much wider scope and reliable results.

Physical and interactive simulations involve the creation of a physical object, usually smaller and/or cheaper than the original, that takes the place of the actual object. For example, aircraft pilots train on flight interactive simulators which are safe and considerably less expensive than an actual plane, especially in case of modern warplanes. **Continuous simulations** refer to a computer model of a physical system built around differential equations in which variables change continuously in function of time and system state is updated continuously. Since it's impossible to represent continuous time flow, time is increased in small steps to simulate the

correct behavior. **Monte Carlo** methods are a class of algorithms that rely on continuous application of random sampling to obtain numerical results. Those methods use randomness to solve problems that originally were deterministic. They usually apply to physical and mathematical problems and are most useful when it is difficult or impossible to use different approaches.

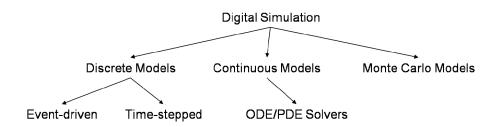

Simulation has been classified into many subcategories that describe the methodologies applied to model the case studies (Fig. 1.1).

Figure 1.1. Simulation Taxonomy

Simulations can be roughly split into the following two categories:

- Stochastic simulations depend on variables drawn from some probability distribution. Any round of the simulation produces different results and, as outputs are produced, final outcomes converge into a distribution of such outputs that is the result in which the simulation with a pre-determined set of values may fall in.

- **Deterministic simulations** are basically the opposite of stochastic ones: values for the variables are fixed and the outcomes are always supposed to be the same.

Actual implementations of the various methods may follow different paradigms. A **distributed simulation** is about distributing a single simulation run across multiple processors.

As described by Fujimoto in [1], there are many advantages in a distributed simulation: in a paradigm known as "parallel execution", the run is performed over a tightly coupled computer system (e.g. a supercomputer or a shared memory multiprocessor) and the main reason for the distribution is to reduce the execution time of the simulation. The great advantage in sharing the execution between N processors stands in the possibility to achieve a theoretical maximum speed increase of (Amdahl's law applied to parallelism)

$$\frac{1}{(1-F) + \frac{F}{N}}$$

compared to a single processor run, where F is the portion of the code that can be parallelized and 1-F the part that remains sequential.

One more advantage resides in the possibility to allow a particularly big execution to run: if limited to a single computer, memory may not be enough to support the execution of that particular run, while distributed execution allows the exploitation of a hugely bigger pool of memory.

A second motivation is the necessity to build a big cooperative simulation environment starting from several different simulators: this necessity can be found for example in military training simulators, flight simulators and various other models where personnel need to train for hypothetical scenarios and situations.

Recently, this kind of simulations has spread into different scopes in modern society. In both military and infrastructure simulations, it is far more convenient to create a bond between existing simulations than to create a brand new one within the context of a single software. Simulation distribution allows personnel to operate remotely through internet and cuts lot of the costs; at the same time, high performance simulations have now the possibility to execute on multiprocessor computers situated in a single cabinet or in a room, as proximity is needed to remove the inefficiencies caused by the delay that occurs during remote communication between processors. The terminology may be confusing: the term "parallel simulation" was once used to qualify simulations executed on a tightly coupled parallel computer, while "distributed simulation" was about physically distributed simulations; with new computer paradigms (e.g. clusters of workstations or grid computing) the distinction became less clear. From now on, "distributed simulation" may refer to both.

One more paradigm is **sequential simulations** and implies a single-threaded execution.

### 1.1 Discrete-event simulation

Discrete-event simulations (DES) manages the execution of the model as a sequence of impulsive events, where every event occurs at a certain time instant and nothing occurs between two of them.

Traditionally, discrete-event simulations employ an inherently sequential algorithm, but large simulation models are limited by this sequentiality because of the limited amount of computing resources which are exploited. An interesting overview by S.Robinson [2] describes DES as one of the most popular modeling techniques that has spread in the '50s and kept evolving until today, where it is applied in visual interactive modeling, simulation optimization, virtual reality, distributed simulation and the worldwide web. DES features the following characteristics:

- Time in DES advances following two possible approaches: fixed-increment time progression, in which time is divided in a series of fixed intervals and the state is updated basing on activities happening between these time slices, and next-event time progressing, the most used as typically runs much faster, in which the simulation time jumps between the timestamps of the processed events.

- A system **state** is needed to keep track of the main properties of the model by keeping a set of explanatory variables. One node can change the current state by **processing events**, and generate new events destined for other nodes in the system as a consequence. Fan-out is a messaging characterization to manage the quantity of events injected inside the system.

- In DES, a clock is used to keep track of the current simulation time by taking into account the instantaneous "hops" caused by events processing.

Every event is timestamped so that the system evolves by processing the events in their timestamp order and it's forbidden for DES models to generate events in the virtual past.

Time is measured by whatever measure unit is chosen by the simulation designer. At least one **pending event set** is required to store and keep track of all those events that are waiting for their turn to be executed. As already stated, every event has his own timestamp and must be executed according to a timestamp-based chronological order over all events.

Usually, these sets take the form of priority queues sorted by event timestamp: the events are inserted in the queues in the order they arrive, but are always picked in strict chronological order.

- The simulation begins with an **initial state** and some default starting events as input; processing these initial events triggers the generation of more events to be injected inside the system. When new events arrive into the input channel of a node, the node itself updates its output and generates new events to be sent to the nodes in its fan-out.

- Ending conditions are determined by the designer, since the simulation may run forever as it could be a model of a physical system. Typically, parameters that determine when simulation should stop are (i) time (i.e. "at time *t* simulation must stop"), (ii) number of processed events and, generally speaking, (iii) when a specific event occurs (e.g. measure *x* is greater than a value *v* or whatever condition over the state, even more complex than this).

- The main loop of the execution is the core of the simulation and repeats the following steps until one of the ending conditions is satisfied. During the first step the "next" event to be processed is picked.

Second step sets the clock to the next slice or to the next-event time, basing on the "time" pattern chosen.

Third step executes the next event and removes it from the event list.

Last step carries out the message delivery procedure that takes the messages to their receivers.

### 1.2 Parallel discrete-event simulation

Parallel computing is a computation technique where processes calculations are carried out simultaneously on different processing units, for example by splitting large problems into smaller ones. Parallelism has been intensively used in highperformance computing in the past, but now is one possible answer to a variety of physical constraints, such as power consumption, that have become a concern for computers in recent years. Power wall and memory wall [3] are two problems that affect evolution in computer infrastructures and that need to be faced. Power wall refers to the theoretical peak of power that a system can sustain: miniaturization of transistors is leading to an extremely high density of them and, consequently, even if modern productive processes achieved a very low electricity consumption over single units, the huge number of simultaneous switching of these transistors causes a tremendous increase of the temperature: more and more expensive cooling systems are asked to keep the hardware at a proper working temperature, a task that is getting very hard to accomplish. In extreme cases, CPU throttling is an automatic system that reduces operating frequencies to avoid damages to the hardware caused by high temperatures.

Memory wall, on the other way, was initially theorized in 1994 by Wulf and McKee. They predicted that sometime in the future, RAM won't be fast enough to keep up the pace of CPUs frequencies; that means that program execution time will depend almost entirely on the speed at which RAM can send data to the CPU. Linked to the memory speed problem, the increase of data size also requires bigger and bigger size of memory over time, and this is actually a different limit to be faced. With these two problems to deal with, distributed execution in general (and PDES in particular), can lighten the weight a single processor must stand by distributing the load of a single execution into many processing units, may they be cores, sets of CPUs or cluster of machines. At the same time, the use of many distributed devices allows systems to access a much bigger pool of memory.

### 1.2.1 Introducing PDES

Many fields of application of DES include real-world scenarios, such as engineering, computer science and military applications.

Parallel Discrete Event Simulation, or PDES, is the parallel (and/or distributed) execution of DES simulations and responds to the always growing necessity to optimize time requirements of such fields of large-scale simulations, other than try to find a solution to problems like "power wall" and "memory wall".

The introduction of parallel computing in DES implies the use of multiple processes or threads, assigned to different CPUs, to perform a single simulation. Of course, the final goal of this distribution is to reduce the execution time and increase the scalability of the simulation.

The infrastructure in which the simulation runs can be divided into two more categories.

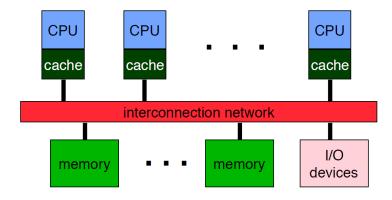

• Shared memory systems (Fig. 1.2), composed by a group of CPUs that share a common memory, are the easiest to implement since communication between different processors is performed on the same memory but, at the same time, contention over shared resources may limit the scalability of the application and introduce synchronization problems.

Figure 1.2. Shared Memory Machines

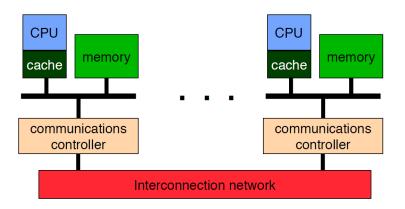

• In a **distributed memory system** (Fig. 1.3), the memory is associated with a set of processors which are only able to access their own memory. Many refer to this kind of architecture as a "multicomputer", since the parts that compose the whole architecture are themselves simple computer systems, complete with processor and memory.

CPUs can only operate on local data, so it's harder to grant synchronization: a message-exchange protocol must be established to regulate the traffic between nodes, keeping into account that external factors, such network delays, may affect the causal consistency over the delivery of messages.

Figure 1.3. Distributed Memory Machines

Distributed Shared Memory (DSM) architectures implement features of both the previous architectures, where physically separated memories appear to the system as a single logically shared address space. Multiple independent nodes have their own memory connected in a shared interconnected network.

The synchronization protocol is invisible for the developers when implemented in an operating system but not when implemented at application level. Actually, in PDES implementations, communication is performed using message passing. The goal of a DSM system is to apply the shared-memory paradigm to a system with physically distributed memory.

DSM systems for PDES have been first studied in [4].

#### 1.2.2 Implementation of synchronization

Thread synchronization is the mechanism that grants two or more threads or processes not to incur into simultaneous execution of some critical section of the code. Control over accesses on those section is performed by synchronization techniques that regulate the flow: basically, when one thread executes the code inside a critical section, the other threads should stop the execution and wait until the previous thread finishes: this is called "mutual exclusion". Lack of control techniques over critical section accesses leads into race conditions where the values for variables may vary in unpredictable ways, basing on the order the threads access to sensible code. Bad synchronization over threads is the origin of many issues such as the followings:

- **Deadlock** is a state of the computation where every member (i.e. thread) stops the execution waiting for some other member to complete a task, such as sending messages or releasing a lock; this happens when the state of a process is unable to change indefinitely because resources it should access to are always under use.

- Starvation happens when a process can never obtain access over a shared resource required to continue the computation: other processes may deny access as consequences of errors in scheduling or in the mutual exclusion algorithm.

Among all the alternatives, there are three main ways to implement synchronization over a multi-processes algorithm.

• **Spinlock**: before accessing a critical section, the processor checks a flag that states if a concurrent process already accessed that area and is still in it; if so, it will wait until this process eventually leaves the critical area and the flag is restored, by spinning in a loop and continuously checking if the flag variable changes (busy waiting). **Busy waiting** is the continuous control over a particular condition (or a series of conditions) to determine if a certain value has changed. Of course, accesses to flags need to be atomic (i.e. to grant integrity, contemporary access by concurrent threads to the resource must be avoided ).

• A **barrier** is a synchronization method applied to a group of threads or processes where a process (or a thread), once incurs in a barrier mechanism, must stop the execution and wait until every process or thread gets into that same part of code.

Barriers may be required in cases where particular areas of the code can be executed only after all the threads performed some required action.

• A semaphore is a structure that controls access to common resources. Every semaphore has a fixed value that says how many processes can enter the critical area. Every time a process requests the access into a section controlled by a semaphore, it checks the counter value: if it is 0, the process must wait, differently it decreases the value by some amount (wait operation) and enters the critical section. When critical operations are over, the process exits from the semaphore-controlled area and increases the value by some amount (signal operation).

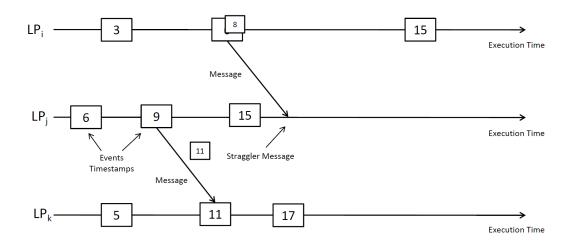

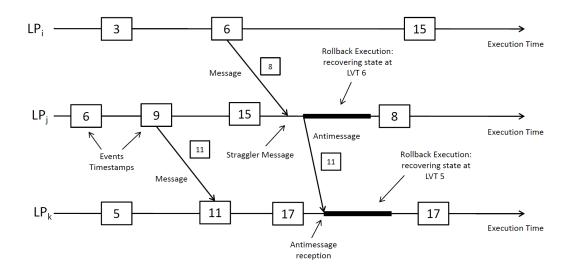

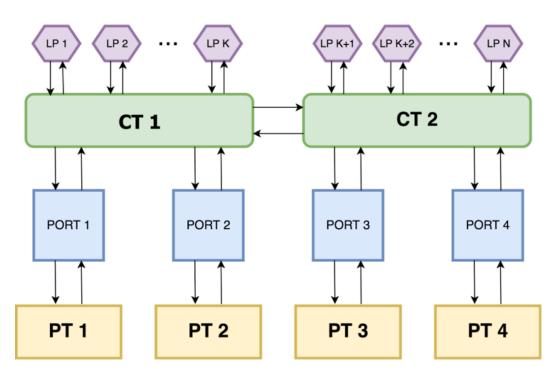

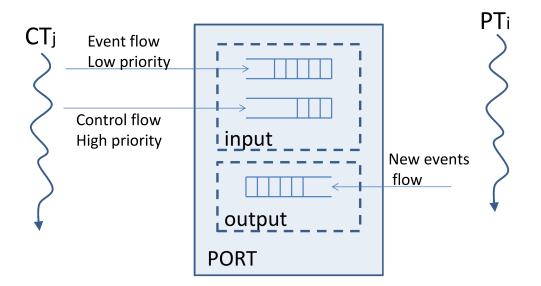

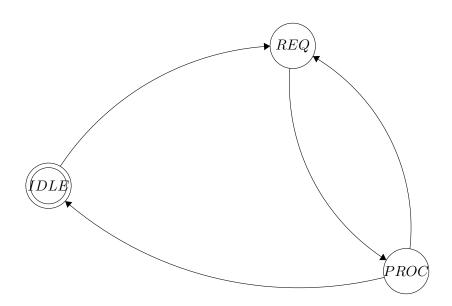

#### 1.2.3 The synchronization problem: stragglers