INTERNATIONAL JOURNAL OF REVIEWS ON RECENT ELECTRONICS AND COMPUTER SCIENCE

# **EFFECTIVE SYSTEM ARCHITECTURE BASED RISC STRATEGY**

Charitha Devi Arika<sup>1</sup>, V. Koteswara Rao<sup>2</sup>

<sup>1</sup>M.Tech Student, Dept of ECE, QIS Institute of Technology, Ongole, A.P, India

<sup>2</sup>Associate Professor, Dept of ECE, QIS Institute of Technology, Ongole, A.P, India

## **ABSTRACT:**

Embedded computers as well as personal computers have become the part and parcel of everyday human life. There is a rapid development in the computer structure. Several computers of different types are developed. Hence there is the deep need to introduce the architecture of the computer to everyone. Every engineer is supposed to know the best about computer. Also a strategy is now being developed to design the Intellectual Property core processors so that anyone could build his own computer/ embedded system as per his specific application. It is possible to build even reconfigurable processors so that the same processor can be reconfigured for different applications. Hence there is the deep need to develop the ability to build one's own processor to meet the needs of one's computing needs. This paper is such an attempt to introduce the RISC based design of processor for pedagogical purposes. This work introduces a processor that can perform all the general tasks such as addiction, subtraction, multiplication, division, AND, OR, XOR, NOT, load and store operations using logic based digital strategy. Embedded system design also becomes simple with the introduction of computer hardware for pedagogical purposes. Extensive testing has been carried out for testing the design and found to give accurate results. The processor is designed with Xilinx ISE 12.1 targeted for porting into the Spartan 6 FPGA kit. The design is quite synthesizable.

Keywords: Logic based on the digital strategy, Processor of the RISC fashion, CPU (central processing unit), Logic based programmable strategy respectively.

### 1. INTRODUCTION

Building a computer/processor from discrete components or ICs is a tough task. Any failure that occurs will cost a lot. Any modification required in between also may partially damage the system. Hence building computers for test/ teaching purposes require automation.

Author [8] made an approach to build computer with MSI components. Authors [6]-[7] designed simple computer using VHDL but lacked understanding of dataflow. Authors [2]-[5] made an approach that allowed interaction. Author [1] implemented RISC based processor with memory but not a full pledged one. Only addition, subtraction were introduced among arithmetic instructions and only AND, NOT and OR logic functions. In this paper a full pledged 8 bit RISC processor architecture is implemented along with RAM and ROM modules. The present design implements all the four arithmetic functions ADDITION, SUBTRACTION, MULTIPLICATION, DIVISION, and all the basic logical operations AND, OR, NOT and XOR operations. It also include load and store operations which are the very characteristic of RISC processors.

The design is implemented in VHDL in Xilinx ISE 12.1 targeted to Spartan 6 FPGA

### **BLOCK DIAGRAM**

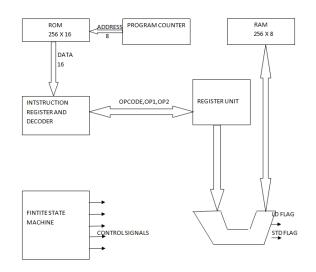

# Fig 1: Shows the block diagram of the present method.

#### 2. METHODOLOGY

There is a huge challenge for the present method where it is supposed to accurately analyze the problems of the several previous methods in a well efficient manner and also used for the theoretical aspect oriented analysis.

The present design is an 8 bit CPU and can execute 23 instructions. It is FSM based design which generates control signals. Instructions are 16 bit wide. Program memory is 16 bit wide. Data memory is 8 bit wide. It has 16 bit program bus and 8 bit program address bus. It has 8 bit data bus and 8 bit data address bus conforming to Harvard architecture. Here the implementation aspect of the present method is shown in the above figure in the form of the block diagram and is explained in the elaborative fashion respectively. Here the present method completely overcomes the shortfalls of the several previous methods in a well efficient manner. Here we finally conclude that the present design oriented mechanism is effective and efficient in terms of the improvement in the system based aspect respectively.

# **3. EXPECTED RESULTS**

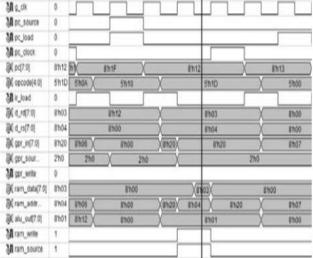

A lot of analysis is made on the present method and the huge number of the simulations has been conducted on the large number of the data sets in a well oriented fashion respectively. Α comparative analysis is made between the present method to that of the several previous methods is shown in the below figure in the form of the graphical representation and explains in a brief elaborative fashion respectively. There is a huge challenge for the present method where it is supposed to improve the performance of the system followed by the overall system based analysis with respect to the outcome of the entire system respectively. The present design is full pledged RISC processor. The simulation

results showing the execution of all the instructions is shown in the figure below.

# Fig 2: Shows the simulation results of the present implementation respectively

# 4. CONCLUSION

In this paper a method is designed with a particular framework oriented strategy to implement the RISC architecture with all basic arithmetic and logical operations. It is used for the improvement in the performance in the system followed by the entire system based outcome. As the design is including all the basic functions of a processor and characteristics of the RISC processor, it is quite ideal for the educational purposes to explain the RISC processor. A lot of observation has been made depending on the platform oriented development based strategy followed by the design orientation of the specifications related to the aspect of the current strategy. Here we finally conclude that the present method is effective and efficient in terms of the performance based strategy followed by the accurate analysis with respect to the entire system based outcome in a well respective fashion respectively.

### REFERENCES

[1] Antonio H. Zavala, Jorge Avante R.,Quetzalcóatl Duarte R., J. David Valencia P."RISC-Based Architecture for Computer Hardware Introduction"

[2] P. Verplaetse, J. Campenhout, "ESCAPE: Environment for the Simulation of Computer Architecture for the Purpose of Education," IEEE TCCA Newsletter, February, pp. 57-59, 1999.

[3] M. Jaumain, M. Osee, A. Richard, A. Vander Biest, P. Mathys, "Educational simulation of the RiSC processor," ICEE

International Conference on Engineering Education, 2007.

[3] G. Wainer, S. Daicz, L. De Simoni, D. Wassermann, "Using the Alfa-1 simulated processor for educational purposes," Journal on Educational Resources in Computing, vol. 1, Issue 4, pp.111–151, 2001

[4] J. Djordjevic, A. Milenkovic, N.Grbanovic, "An Integrated Environment for Teaching Computer Architecture," IEEE Micro vol.20, Issue 3, pp. 66–74, 2000.

[5] D. Mandalidis, P. Kenterlis, J. Ellinas, "A computer architecture educational system based on a 32-bit RISC processor," International Review on computers and Software, pp. 114-119, 2008.

[6] M. Becvar, A. Pluhacek, J. Danecek, "DOP: a CPU core for teaching basics of computer architecture," Workshop on Computer architecture education, Article No. 4, 2003.

[7] H. ElAarag, "A complete design of a RISC processor for pedagogical purposes," Journal of Computing Sciences in Colleges, vol. 25, Issue 2, pp. 205-213, 2009.

[8] Pattersson, Hennessy, ComputerOrganization and Design, Thehardware/software interface, 2nd Edition,Morgan Kaufmann, 1998.

[9] Tocci, Widmer, Moss, "Sistemas Digitales, Principios y aplicaciones," 10<sup>a</sup> Edición, Pearson, 2007. [10] W. Stallings, "Organización y Arquitectura de Computadoras," 7<sup>a</sup> Edición, Pearson, 2006.

[11] M. Mano, "Arquitectura de computadoras," 3ª Edición, Pearson, 1994.

# **AUTHORS:**

1. Charitha Devi Arika is a final year student of M.Tech in VLSI and embedded systems from QIS Institute of technology, Ongole affiliated to JNTU, Kakinada.

Sri V. Koteswara Rao received his B.Sc, degree from Andhra University, waltair. He received his AMIETE degree in electronics and communication engineering

from IETE, India. He received his M.Tech in Embedded Systems and VLSI design from JNTU, Hyderabad. He is a member of IEEE, USA., Fellow of IETE., India and a Professional member of ACM, USA. He worked for AP state govt., India as Deputy Executive Information Engineer for several years. He is presently working as Associate professor, in ECE department of QIS Institute of technology, Ongole, AP, india. He is presently also a research scholar in VLSI at Vignan University, Vadlamudi, Guntur Dt., AP., India.