# Infrastructure for DEVS Modelling and Experimentation

Hongyan Song Supervisor : Prof. Hans Vangheluwe

School of Computer Science McGill University, Montréal, Canada

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfilment of the requirements of the degree of Master of Science in Computer Science

Copyright ©2006 by Hongyan Song All rights reserved

#### **Abstract**

After over thirty years of research and development, Discrete EVent system Specification (DEVS) has been widely accepted and applied in the Modelling and Simulation community. Recently, standardizing DEVS formalism and expanding DEVS application have become major chellanges for DEVS researchers. In this thesis, we present our efforts to facilitate the process of DEVS modelling, and to promote DEVS standardization and application.

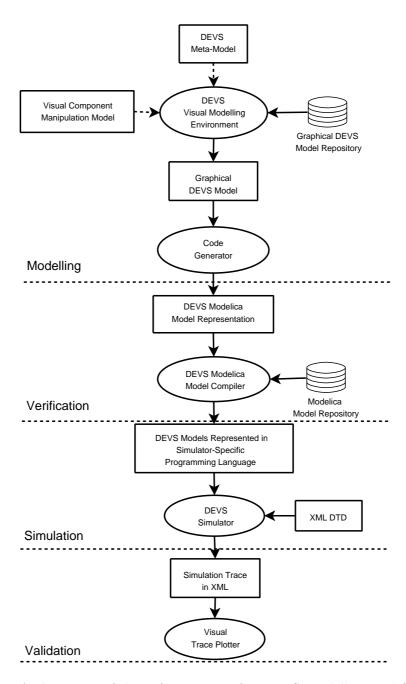

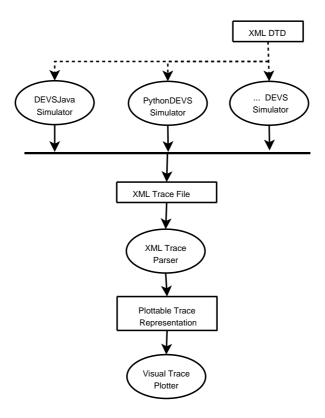

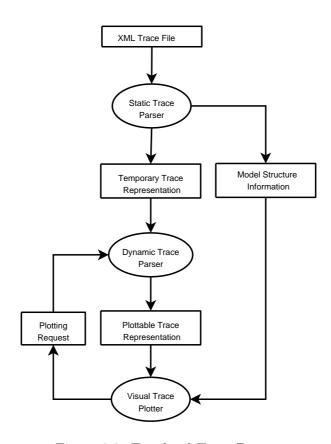

The Infrastructure for DEVS Modelling and Exmperimenting provides facilities to facilitate the DEVS modelling process at four different levels. At the modelling level, a visual DEVS modelling environment has been built, in which DEVS models can be created graphically, and simulator-neutral model representation in modelling language Modelica can be generated automatically. At the model verification level, a Modelica Model Compiler has been developed, by which the simulator-neutral model representations are checked automatically and translated into simulator-specific model representations. At the simulation level, simulation trace has been standardized using the XML DTD. Interfaces for generating standardized simulation trace represented in XML for Python DEVS has been provided. At the model validation level, a Visual DEVS Trace Plotter has been developed, by which the standardized DEVS simulation trace in XML can be plotted visually.

Après plus de trente ans de recherche et de développement, les spécifications de système discrètes d'événement (DEVS), ont été largement acceptées et appliquées dans la communauté de modelage et de simulation. Récemment, la normalisation du formalisme de DEVS et les extensions de l'application de DEVS sont devenus des défis principaux pour les chercheurs de DEVS. Dans cette thèse, nous présentons nos efforts de faciliter le processus de modelage en DEVS, et de favoriser la normalisation et l'application de DEVS.

L'infrastructure pour le modelage et expérimentation de DEVS fournit des équipements pour faciliter le processus de modelage de DEVS à quatre niveaux différents. Au niveau modelant, un environnement de modelage visuel de DEVS a été construit. Cet environnement permet la création des modèles graphiques de DEVS aussi bien que la génération automatique d'une représentation de modèle simulateur-neutre dans la langue modelante Modelica. Au niveau de la vérification de modèle, un compilateur de modèle de Modelica a été développé, par lequel les représentations des modèles simulateur-neutres sont vérifiées automatiquement et traduites en représentations de modèles simulateur-spécifiques. Au niveau de la simulation, la trace de simulation a été normalisée en utilisant le XML DTD. Des interfaces pour produire une trace normalisée de simulation représentée dans XML pour le Python DEVS ont été fournies. Au niveau de la validation de modèle, un traceur visuelle de trace de DEVS a été développée pour tracer visuellement la trace normalisée de simulation de DEVS.

## Acknowledgements

Some parts of this thesis are based on previous works done in the MSDL (Modelling, Simulation, and Design Lab) at McGill University. I would like to express my sincere gratitudes to people who have made contributions to this thesis.

First, many thanks to my supervisor Prof. Hans Vangheluwe. His insight and passion in the modelling and simulation are the keys to the success of this thesis.

Thanks to Steven Xu's  $\mu$ Modelica compiler and help on reusing components of that compiler.

Thanks to Denis Dube's original DEVS meta-model and help on using State Charts in AToM<sup>3</sup>.

Thanks to Ernesto Posse's ideas on Python DEVS code generation in  ${\rm AToM^3}$  and help on system maintenance.

And finally, thanks to people who have read and commented on this thesis.

## Contents

| 1        | Disc | crete EVent system Specification (DEVS) Formalism | 5  |

|----------|------|---------------------------------------------------|----|

|          | 1.1  | Introduction                                      | 5  |

|          | 1.2  | Discrete Event System Specification               | 7  |

|          |      | 1.2.1 Classic DEVS                                | 7  |

|          |      | 1.2.2 Clarification of Concepts                   | 10 |

|          |      | 1.2.3 Parallel DEVS                               | 11 |

|          | 1.3  | Abstract DEVS Simulation Engine                   | 14 |

|          |      | 1.3.1 Abstract Simulator for Classic DEVS         | 14 |

|          |      | 1.3.2 Abstract Simulator for Parallel DEVS        | 18 |

|          | 1.4  | DEVS modelling and Simulation Environments        | 23 |

|          |      | 1.4.1 PythonDEVS                                  | 23 |

|          |      | 1.4.2 DEVSJava                                    | 26 |

|          |      | 1.4.3 ADEVS                                       | 27 |

|          | 1.5  | Conclusions                                       | 28 |

| <b>2</b> | Arcl | hitecture and Design                              | 29 |

|          | 2.1  | Introduction                                      | 29 |

|          | 2.2  | Modelling Language Concepts                       | 32 |

|          |      | 2.2.1 Modelling                                   | 32 |

|          |      | 2.2.2 Modelling Language                          | 32 |

|          |      | 2.2.3 Meta-modelling                              | 33 |

|          |      | 2.2.4 Simulation                                  | 35 |

|          |      | 2.2.5 Verification                                | 35 |

|          |      | 2.2.6 Validation                                  | 36 |

|          |      | 2.2.7 Modelling and Simulation Process            | 36 |

|          | 2.3  | Motivation and Purpose                            | 38 |

|          | 2.4  | The Overall Architecture                          | 41 |

|          | 2.5  | Conclusions                                       | 45 |

| 3        | Star | ndardized Trace Representation and Trace Plotter  | 47 |

| -        | 3.1  | Introduction                                      | 47 |

|          | 3.2  | Design and Implementation                         | 49 |

|   |      | 3.2.1 Architecture of the Trace Plotter                              |

|---|------|----------------------------------------------------------------------|

|   |      | 3.2.2 XML DTD for Trace Output                                       |

|   |      | 3.2.3 Trace Parser                                                   |

|   |      | 3.2.4 Visual Trace Plotter                                           |

|   | 3.3  | Case Study                                                           |

|   |      | 3.3.1 XML Represented Trace for the Processer Model 62               |

|   |      | 3.3.2 Plotting Trace Using the Simple Plotter                        |

|   |      | 3.3.3 Plotting Trace Using the Customized Plotter                    |

|   | 3.4  | Conclusions                                                          |

| 4 | Mod  | delica Representation and Model Compiler 67                          |

|   | 4.1  | Introduction                                                         |

|   | 4.2  | Modelica and Its Model Description Constructs                        |

|   | 4.3  | Design and Implementation                                            |

|   |      | 4.3.1 The Architecture                                               |

|   |      | 4.3.2 Representing DEVS in Modelica                                  |

|   |      | 4.3.3 Representing DEVS Components in Modelica                       |

|   |      | 4.3.4 Using Language-Specific Library Functions in Modelica 79       |

|   |      | 4.3.5 The Model Compiler: from Modelica to PythonDEVS 80             |

|   |      | 4.3.6 Python DEVS Code Generator                                     |

|   | 4.4  | Case Study                                                           |

|   | 4.5  | Conclusions                                                          |

| 5 | Visu | ual DEVS Modelling Environment 93                                    |

|   | 5.1  | Introduction                                                         |

|   | 5.2  | Modelling and Meta-Modelling in $AToM^3$                             |

|   | 5.3  | Design and Implementation                                            |

|   |      | 5.3.1 Architecture                                                   |

|   |      | 5.3.2 Meta-Modelling DEVS in AToM <sup>3</sup>                       |

|   |      | 5.3.3 User Interface Model - State-chart                             |

|   | 5.4  | Code Generator: from Visual Model to Modelica                        |

|   |      | 5.4.1 Mapping Visual Model Components to Modelica Representation 102 |

|   |      | 5.4.2 Atomic DEVS Code Generator                                     |

|   |      | 5.4.3 CoupledDEVS Code Generator                                     |

|   |      | 5.4.4 Event Generator                                                |

|   | 5.5  | Case Study                                                           |

|   | 5.6  | Conclusions                                                          |

| 6 | Case | e Study 113                                                          |

|   | 6.1  | Introduction                                                         |

|   | Bibli | iograph  | цу                                          | 137 |

|---|-------|----------|---------------------------------------------|-----|

| 7 | Con   | clusions | s and Future Work                           | 133 |

|   | 6.7   | Trace    | Plotting Using Visual Trace Plotter         | 131 |

|   | 6.6   | Simula   | ation Trace                                 | 129 |

|   |       | 6.5.4    | The Experiment Model                        | 127 |

|   |       | 6.5.3    | Coupled Multi-Processors                    | 126 |

|   |       | 6.5.2    | Atomic Processor                            | 123 |

|   |       | 6.5.1    | Job Event                                   | 123 |

|   | 6.5   | Pytho    | n DEVS Representation                       |     |

|   |       | 6.4.4    | The Experiment Model                        |     |

|   |       | 6.4.3    | Chained Processors - Root                   | 121 |

|   |       | 6.4.2    | Atomic Processor                            |     |

|   |       | 6.4.1    | Job Event                                   |     |

|   | 6.4   | The M    | Iodelica Representation                     |     |

|   |       | 6.3.4    | Experiment Model                            |     |

|   |       | 6.3.3    | The Coupled DEVS Model - Chained Processors |     |

|   |       | 6.3.2    | Atomic Processor                            |     |

|   |       | 6.3.1    | Job Event                                   |     |

|   | 6.3   | The V    | isual Models                                |     |

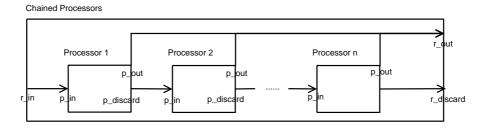

|   |       | 6.2.2    | The Chained-Processor Model                 | 115 |

|   |       | 6.2.1    | The Processor Model                         |     |

|   | 6.2   | DEVS     | Models of the Chained-Processor System      | 114 |

# List of Figures

| 1.1  | Mapping between DEVS Models and Simulators                           | 14 |

|------|----------------------------------------------------------------------|----|

| 1.2  | Messages Used in Classic DEVS Coordinators and Simulators            | 15 |

| 1.3  | Messages for Parallel DEVS Coordinators and Simulators               | 19 |

| 1.4  | Prototypes of Python DEVS Models                                     | 23 |

| 1.5  | Fully Qualified Name in Python DEVS                                  | 24 |

| 1.6  | Class Diagram of the Python DEVS Simulator                           | 24 |

| 1.7  | The Inheritance Diagram of DEVSJava                                  | 25 |

| 1.8  | Class Diagram of DEVS Java                                           | 25 |

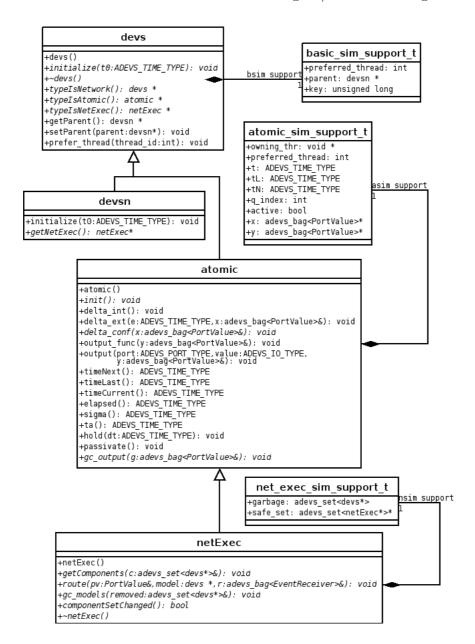

| 1.9  | Class Diagram of ADEVS                                               | 26 |

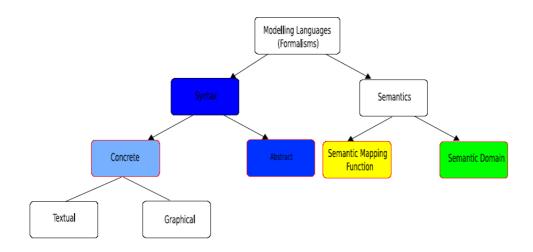

| 2.1  | Modelling Language Breakdown                                         | 32 |

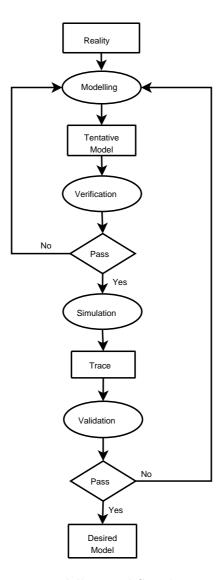

| 2.2  | Modelling and Simulation Process                                     | 37 |

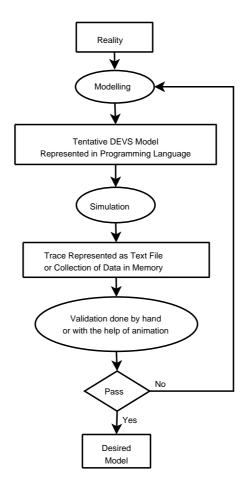

| 2.3  | Current General Practice of DEVS Modelling and Simulation Process    | 38 |

| 2.4  | Architecture of the Infrastructure for DEVS Modelling and Simulation | 41 |

| 3.1  | Architecture of the Trace Plotter                                    | 49 |

| 3.2  | Fully Qualified Model Name                                           | 52 |

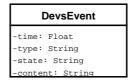

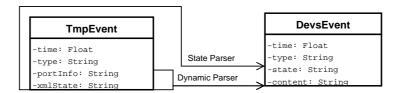

| 3.3  | Two-level Trace Parser                                               | 53 |

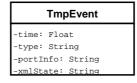

| 3.4  | Temporary Trace Representation                                       | 54 |

| 3.5  | Plottable Trace Representation                                       | 55 |

| 3.6  | Class Diagram of the Static Trace Parser                             | 55 |

| 3.7  | Parsing TmpEvent into DevsEvent                                      | 57 |

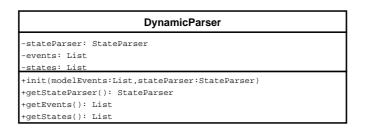

| 3.8  | Class Diagram of Dynamic Parser                                      | 57 |

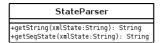

| 3.9  | State Parser                                                         | 58 |

| 3.10 | Simple State Parser                                                  | 58 |

| 3.11 | Visual Trace Plotter                                                 | 59 |

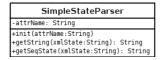

| 3.12 | Terms Used in Trace Plotter                                          | 60 |

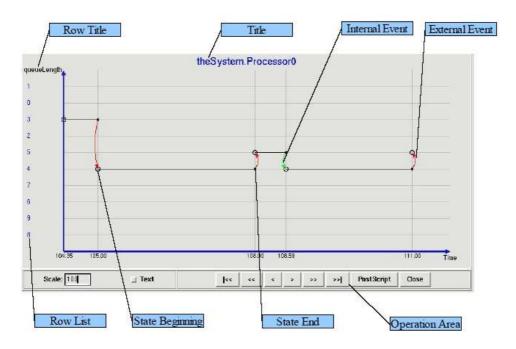

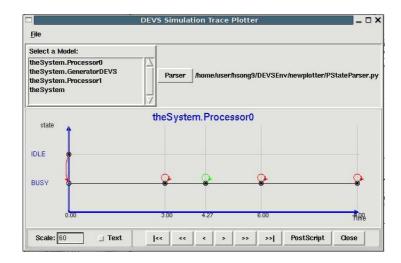

| 3.13 | Plotting Trace Using the Simple Plotter                              | 62 |

| 3.14 | Plotting Trace Using the Customized Plotter                          | 63 |

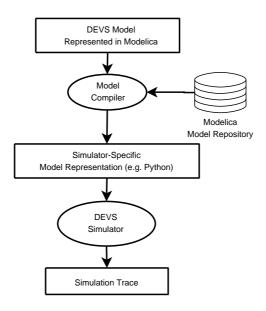

| 4.1  | Architecture for Modelica based DEVS Modelling and Simulation        | 74 |

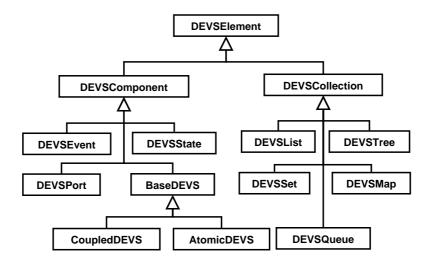

| 4.2  | Predefined DEVS Elements in Modelica                                 | 75 |

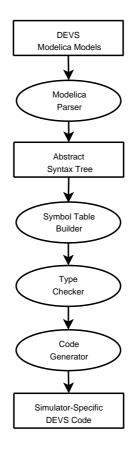

| 4.3 | The Architecture of DEVS Modelica Compiler          | 81  |

|-----|-----------------------------------------------------|-----|

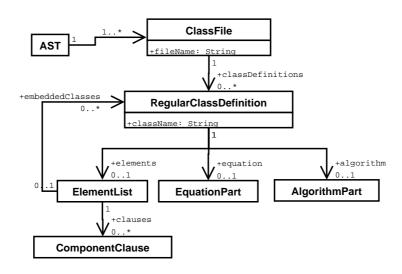

| 4.4 | The Modelica Abstract Syntax Tree Structure         | 84  |

| 4.5 | The Class Diagram of Python DEVS Generator          | 85  |

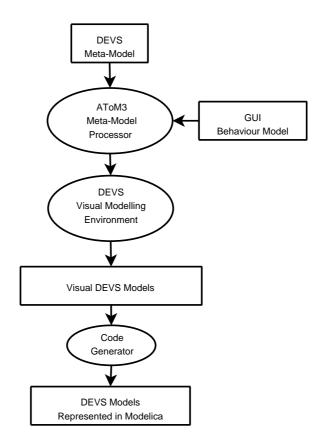

| 5.1 | Architecture of DEVS Visual Modelling Environment   | 97  |

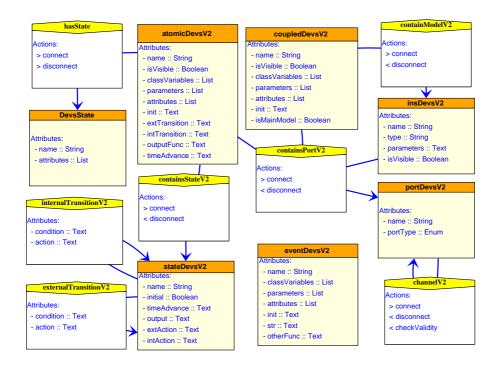

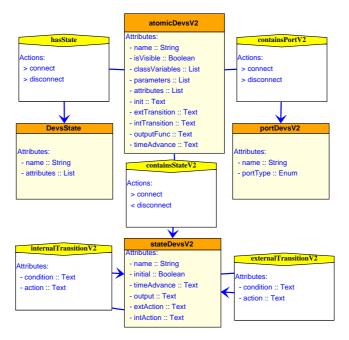

| 5.2 | DEVS Meta-Model                                     | 98  |

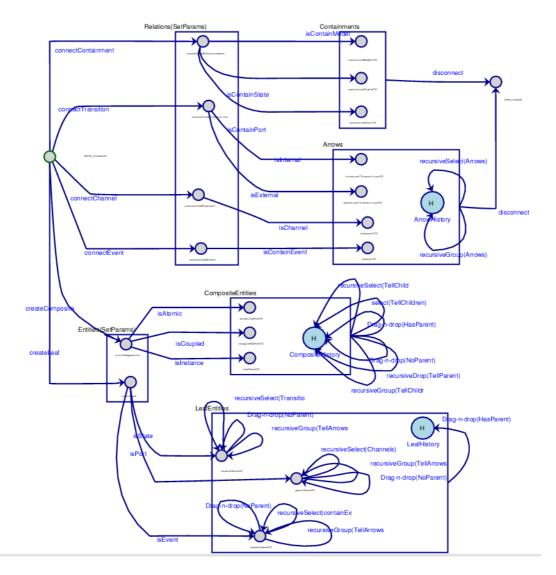

| 5.3 | State Chart for DEVS Visual Modelling GUI Interface | 100 |

| 5.4 | Meta-Model for Atomic DEVS Model                    | 103 |

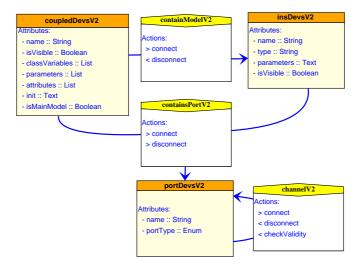

| 5.5 | Meta-Model for Coupled DEVS Model                   | 107 |

| 5.6 | Meta-Model for DEVS Event                           | 108 |

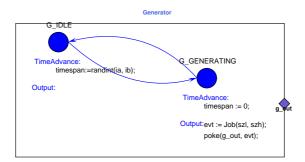

| 5.7 | An Example of Visual Atomic DEVS Model - Generator  | 109 |

| 6.1 | Coupled Model for the Chained-Processor System      | 115 |

| 6.2 | DEVS Event - Job                                    | 117 |

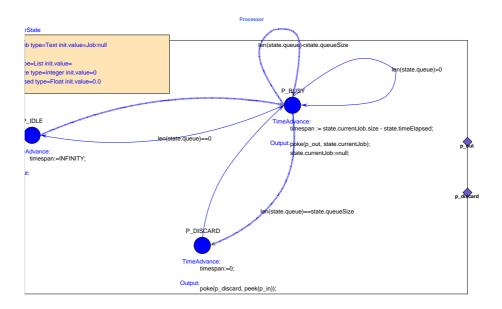

| 6.3 | Atomic DEVS Model - Processor                       | 117 |

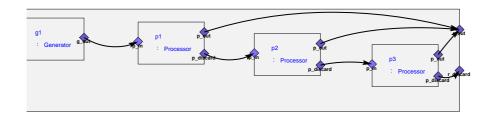

| 6.4 | Coupled DEVS Model - Chained Processors             | 118 |

| 6.5 | An Example of a DEVS Simulation Experiment          | 118 |

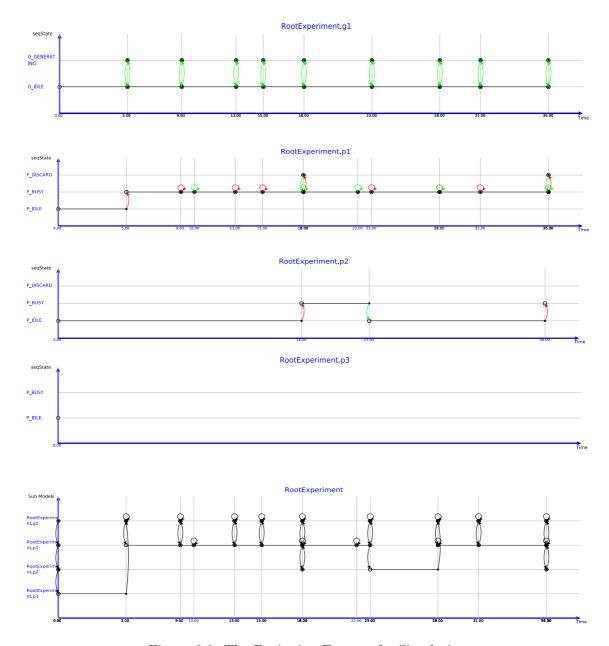

| 6.6 | The Beginning Events of a Simulation                | 131 |

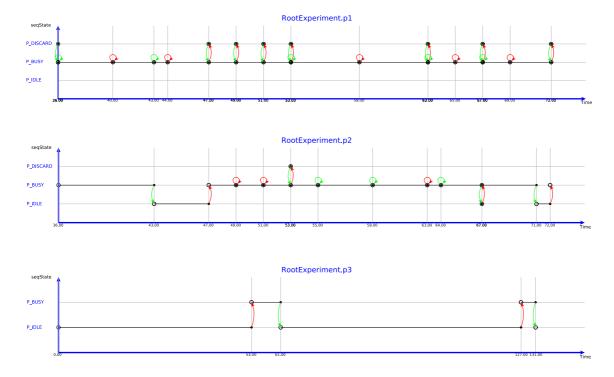

| 6.7 | Simulation Trace That All Processors Having Jobs    | 132 |

# List of Tables

| 3.1 | Values of modelEvents for Example 3.1 | 56 |

|-----|---------------------------------------|----|

| 3.2 | Values of coupleComp                  | 56 |

### Introduction

Differential equations have been commonly accepted as a standard modelling formalism for describing continuous-time dynamic systems for many years. However, though there are many formalisms used for representing discrete event systems, there is still no consensus on a commonly accepted one for discrete event modeling.

Ho [Y.C89] lists the following challenges that must be addressed when one tries to develop a universally applicable modelling framework for Discrete Event Dynamic Systems (DEDS):

- 1. The discontinuous nature of Discrete Events

- 2. The continuous nature of most Performance Measures

- 3. The importance of Probabilistic Formulation

- 4. The need for hierarchical modelling

- 5. The presence of Dynamics as well as Structure

- 6. The feasibility of the Computational Burden

- 7. The need for both experimental and theoretical components

Zeigler [ZV93] claims that a system theoretic framework can provide a solid modeling foundation for addressing these issues in a unified manner. He further argues that discrete event simulation models can be captured as a subclass of systems using the Discrete EVent system Specification (DEVS) formalism, which is built on system theory.

DEVS was first proposed by Zeigler in the 1970's [ZPK00]. As a mathematical basis for discrete event modelling, DEVS provides not only a formal representation of discrete event dynamic systems that is independent of any computer realization, but also a guidline for how to build abstract DEVS simulation engines to simulate the models. Since its inception, DEVS has attracted a lot of attention, though no standard has emerged yet.

After over thirty years of research and development, the DEVS formalism has been extended from its original formalism currently known as Classic DEVS[Van04], which only supports sequential discrete event modelling and simulation, to Parallel DEVS, CELL-DEVS, Dynamic DEVS, Real-time DEVS and so forth[ZPK00]. Many DEVS modelling and simulation evironments, such as DEVSJava[Zei05], Python DEVS[BV02], and ADEVS[Nut05] have been designed and implemented. With the support of so many tools, DEVS has been applied in many different fields. [ZKB99] introduces an approach of distributed supply chain modelling using Parallel DEVS; [AEA+02] presents a method of modelling fire spreading using Cell-DEVS; and [SK94] proposes ideas of modelling a water supply system using DEVS.

The major goal of modelling and simulation is to facilitate the understanding of the system under study. To achieve the goal of DEVS modelling and simulation, we first have to build convenient tools to make DEVS modelling and simulation easy to use and to be understood. There are many efforts in this direction. [PP93] presents visual modelling of DEVS using higraphs; [HK06] introduces a specification language DEVSpecI for DEVS model representation; [AHW05] and [ST00] propose ideas on trace visualization for studying complex systems.

In this thesis, we present our efforts to facilitate and promote DEVS modelling and simulation – an Infrastructure for DEVS Modelling and Experimentation. At the modelling level, we use

meta-modelling and a visual modelling language to construct a visual DEVS modelling environment. In this approach, we not only build a meta-model for DEVS, but also our entire modelling environment is modeled. At the textual model representation level, we describe our models in Modelica[Fri04], which is a popular model description language for both continuous and discrete models, and use a Model Compiler to translate the simulator-neutral Modelica represented models into programming language-specific simulation models. At the simulation level, we standardize the trace representation in XML, and build a generic Visual Trace Plotter which can plot any trace that follows the XML trace description DTD.

The organization of this thesis is as follows. In chapter 1, we first review the Discrete EVent system Specification formalism and some of its popular variants. In chapter 2, we discuss the design architecture of the Infrastructure, in which a big picture of the whole system is given. In chapter 3, 4, and 5, we presents the sub-systems of the Infrastructure. In chapter 3, we introduce DEVS simulation trace standardization and the Visual Trace Plotter. In chapter 4, we discuss representing DEVS models in Modelica and the Model Compiler, which compiles models described in Modelica into models represented in Python DEVS. In chapter 5, we presents issues of meta-modelling the DEVS formalism, building a visual DEVS models. In chapter 6, we give a case study, in which an example demonstrating the whole process of building DEVS models using the Infrastructure is discussed. Finally, in chapter 7, we draw conclusions on the Infrastructure and talk about further efforts to improve the Infrastructure.

# 1

# Discrete EVent system Specification (DEVS) Formalism

#### 1.1 Introduction

DEVS (Discrete EVent system Specification) was first proposed by Zeigler in the 1970's as a mathematical basis for deterministic discrete event modelling ([ZPK00]). DEVS provides a formal representation of discrete event dynamic systems that is capable of mathematical operation and independent of any computer realization. In DEVS, a complex system can be specified by two different kinds of models, atomic models and coupled models. Atomic models can be connected together to form coupled models. The composed coupled models and atomic models can be further connected to create more complex hierarchical coupled models.

Atomic models are the basic units in DEVS[Van04]. The structure of atomic models is described as components with inputs, states, and outputs. The behaviour of an atomic model is specified by functions that reflect the state change and output to the environment of the model corresponding to different inputs. The input and output concepts in atomic DEVS have two levels of meaning. First, each model may have input and output ports, by which the model can interact with its environment. Second, what can go through the ports are input events that the environment sends to the model and output events that the model sends back to the environment. The input and output in an atomic model mean not only events but also ports through which events come in or send out. The modularity of the atomic models comes from the port concept, by which the implementation of an atomic model only needs to consider the input events coming from its input ports and send its output to appropriate output ports. Issues such as how events come to input ports and how to send an event to other models do not need to be considered at the atomic model level.

The states specified in an atomic model are called sequential states, which are not the complete model states. They actually represent identifications of discrete model state space partitions[PP93], which means that the state space of an model can be partitioned exclusively into many different parts, and each of them is identified by a name (sequential state). The behaviour of a model can be seen as the model staying at different sequential states. Within different sequential states, the model can react to different events or react differently to the same events. After processing an event, the model may changes its state.

The behaviour of a model changing its sequential state from one to another is called state transition. How a model does its state transitions is determined by its transition functions. Input events lead to "external event transitions", which means that upon occurrence of an input event, whether the model transits to another state and how to transit to another state is determined by the external event transition function. The time interval a model stays in a

particular state in the absence of external events is determined by the *time advance function*. When this time has elapsed, an event is triggered. The time scheduled events are called internal events. Upon the occurrence of an internal event, the model produces an output event by its *output function* and transits to a new state determined by its *internal state transition function*.

Atomic DEVS models can be coupled together by connecting their input and output ports to build a coupled model. Coupled models have their own input and output ports, which can be used to connect other coupled or atomic models to create even larger hierarchical models. When used to connect to other models, coupled models are not distinguishable from atomics models, so they are reusable to build hierarchical models in the same way as atomic components.

Since its inception, DEVS has been studied over 30 years. The specification has evolved and been extended by many researchers. The original version is now called Classic DEVS, and the latest edition is called Parallel DEVS ([ZPK00], [AB94], [Van04]). The major difference between Classic DEVS and Parallel DEVS is the way they deal with transition collisions. Classic DEVS does not provide any mechanism of processing transition collisions at atomic level. It is the task of the select function of a coupled model to break the tie between simultaneous transitions. In Parallel DEVS, transition collisions have been broken by the *confluent transition function* at atomic level. So there is no need at coupled level to process simultaneous transitions (see section 1.2.2).

In addition to Classic DEVS and Parallel DEVS, there are many other extended versions of DEVS. The most significant extensions are Cell-DEVS ([WG01a], [WG01b]), and Dynamic Structure DEVS (DSDEVS) ([Bar97], [Uhr01]). Cell-DEVS makes DEVS more efficient in modelling phenomena that are suitable for state space partitioning. DSDEVS makes it possible for DEVS to model situations that include dynamic structure changes.

One advantage of DEVS is that it provides not only a modular, hierarchical modelling framework, but also a concept of abstract simulator (i.e., operational semantics), by which the model behaviour can be generated. There are many different implementations of DEVS modelling and simulation tools available now ([Zei05], [BV02], [Nut05]). Each one has its own features and functionalities. We will investigate some of them to get a flavour of the difference.

The Modelling and Simulation industry in nature has a tight relationship with computer and software development technology. During the time of DEVS evolution significant progress has been made in the software engineering industry. From the software design point of view, structural software design has gradually finished its mission, object-oriented software development and model driven architechure become more and more populer. From a computing language aspect, much effort is spent on the research of visual language and software visualization. Though these new trends have not reached the level that can replace all the tranditional technologies, they can potentially promote and facilitate the development and application of modelling and simulation technology. In this thesis, we present an infrastructure we built for facilitating DEVS visual modelling and experimentation, in which some new technologies like visual metamodelling, and visual languages are used. Before we further discuss our infrastructure, let us review some related background about DEVS.

We will first discuss the basic DEVS formalisms, Classic DEVS and Parallel DEVS. Then we will look into algoritms for DEVS simulators. After that, we will present the features of some implementations of DEVS modelling and simulation tools. We will use DEVSJava, ADEVS, and Python DEVS as examples to explain the features and differences.

#### 1.2 Discrete Event System Specification

The DEVS formalism fits the general structure of deterministic, causal systems in classical systems theory. DEVS allows for the description of system behaviour at two levels. At the lowest level, an atomic DEVS describes the autonomous behaviour of a discrete-event system as a sequence of deterministic transitions between sequential states as well as how it reacts to external input (events) and how it generates output (events). At the higher level, a coupled DEVS describes a system as a network of coupled components. The components can be atomic DEVS models or coupled DEVS in their own right. The connections denote how components influence each other. In particular, output events of one component can become, via a network connection, input events of another component. The DEVS formalism is closed under coupling: for each coupled DEVS, a resultant atomic DEVS can be constructed ([Zei84]). As such, any DEVS model, be it atomic or coupled, can be replaced by an equivalent atomic DEVS. The construction procedure of a resultant atomic DEVS is also the basis for the implementation of an abstract simulator or solver capable of simulating any DEVS model. As a coupled DEVS may have coupled DEVS components, hierarchical modelling is supported.

To be suitable for simulation under simulators implemented in different architectures, there are basically two types of DEVS specifications. Classic DEVS specifies models that are suitable for simulation under sequential DEVS simulators. Parallel DEVS defines models that are amenable to parallel simulation.

#### 1.2.1 Classic DEVS

#### Classic Atomic DEVS Formalism

The atomic DEVS formalism is a structure describing the different aspects of the discrete-event behaviour of a system([ZPK00]):

$$AtomicDEVS \equiv (X, Y, S, \delta_{ext}, \delta_{int}, \lambda, t_a)$$

The time base T is continuous and is not mentioned explicitly [Van04]

$$T = \mathbb{R}$$

.

Each atomic DEVS model has a set of input events X, a set of output events Y, and a set of sequential states S. The model transits its state through state transition functions. Upon arrival of an input event x, the new state is determined by the return value of  $\delta_{ext}((s, e), x)$ , which means that the new state is determined by the current state s, the time it stays at s, and the input event x. When there is no external event, the time interval the model stays on its current state is determined by applying the  $t_a$  function to the current state. And the next state of the model is determined by  $\delta_{int}(s)$ , where s is the current state. Just before an internal state transition, the model can generate an output event by applying the  $\lambda$  function to the current state s, i.e.  $\lambda(s)$ . Details on each part of the formalism are explained as below.

The state set S is the set of sequential states: the DEVS dynamics consists of an ordered sequence of states from S. Typically, S will be a structured set (a product set)

$$S = \times_{i=1}^{n} S_i$$

This formalizes multiple (n) concurrent parts of a system. It is noted how a structured state set is often synthesized from the state sets of concurrent components in a coupled DEVS model.

The time the system remains in a sequential state before making a transition to the next sequential state is modelled by the time advance function

$$t_a: S \to \mathbb{R}^+_{0, +\infty}.$$

As time in the real world always advances, the image of  $t_a$  must be non-negative numbers.  $t_a=0$  allows for the representation of instantaneous transitions: no time elapses before transition to a new state. Obviously, this is an abstraction of reality which may lead to simulation artifacts such as infinite instantaneous loops which do not correspond to real physical behaviour. If the system is to stay in an end-state s forever, this is modelled by means of  $t_a(s)=+\infty$ .

The internal transition function

$$\delta_{int}: S \rightarrow S$$

models the transition from one state to the next sequential state.  $\delta_{int}$  describes the behaviour of a Finite State Automaton;  $t_a$  adds the progression of time.

It is possible to observe the system output. The output set Y denotes the set of admissible outputs. Typically, Y will be a structured set (a product set)

$$Y = \times_{i=1}^{l} Y_i$$

This formalizes multiple (l) output ports. Each port is identied by its unique index i. In a user-oriented modelling language, the indices would be derived from unique port names.

The output function

$$\lambda: S \to Y \cup \{\emptyset\}$$

maps the internal state onto the output set. Output events are only generated by a DEVS model at the time of an internal transition. At that time, the state before the transition is used as input to  $\lambda$ . At all other times, the non-event  $\emptyset$  is output.

To describe the total state of the system at each point in time, the sequential state  $s \in S$  is not sufficient. The elapsed time e since the system made a transition to the current state s needs also to be taken into account to construct the total state set

$$Q = \{(s, e) \mid s \in S, \ 0 \le e \le t_a(s)\}$$

The elapsed time e takes on values ranging from 0 (transition just made) to  $t_a(s)$  (about to make transition to the next sequential state). Often, the time left  $\sigma$  in a state is used:

$$\sigma = t_a(s) - e$$

Up to now, only an autonomous system was described: the system receives no external inputs. Hence, the input set X denoting all admissible input values is defined. Typically, X will be a structured set (a product set)

$$X = \times_{i=1}^{m} x_i$$

This formalizes multiple (m) input ports. Each port is identied by its unique index i. As with the output set, port indices may denote names.

The set  $\Omega$  contains all admissible input segments  $\omega$

$$\omega: T \to X \cup \{\emptyset\}$$

In discrete-event system models, an input segment generates an input event different from the non-event  $\emptyset$  only at a finite number of instants in a bounded time-interval. These external events, inputs x from X, cause the system to interrupt its autonomous behaviour and react in a way prescribed by the external transition function

$$\delta_{ext}: Q \times X \to S$$

The reaction of the system to an external event depends on the sequential state the system is in, the particular input and the elapsed time. Thus,  $\delta_{ext}$  allows for the description of a large class of behaviours typically found in discrete-event models (including synchronization, preemption, suspension and re-activation).

When an input event x to an atomic model is not listed in the  $\delta_{ext}$  specification, the event is ignored.

#### Classic Coupled DEVS

The coupled DEVS formalism describes a discrete-event system in terms of a network of coupled components [Van04].

$$CoupledDEVS \equiv \langle X_{self}, Y_{self}, D, \{M_d\}, \{I_d\}, \{Z_{i,d}\}, Select \rangle,$$

The component self denotes the coupled model itself.  $X_{self}$  is the (possibly structured) set of allowed external inputs to the coupled model.  $Y_{self}$  is the (possibly structured) set of allowed (external) outputs of the coupled model. D is a set of unique component references (names). The coupled model itself is referred to by means of self, a unique reference not in D.

The set of components is

$$\{M_i \mid i \in D\}.$$

Each of the components must be an atomic DEVS

$$M_i = (X_i, Y_i, S_i, \delta_{\text{ext},i}, \delta_{\text{int},i}, \lambda_i, t_{\text{a},i}), \forall i \in D$$

The set of inuencees of a component, the components influenced by  $i \in D \cup \{self\}$  is  $I_i$ . The set of all influencees describes the coupling network structure

$$\{I_i \mid i \in D \cup \{self\}\}\$$

For modularity reasons, a component (including self) may not influence components outside its scope the coupled model, rather only other components of the coupled model, or the coupled model self:

$$\forall i \in D \cup \{self\}: Ii \subseteq D \cup \{self\}$$

This is further restricted by the requirement that none of the components (including self) may influence themselves directly as this could cause an instantaneous dependency cycle (in case of a 0 time advance inside such a component) akin to an algebraic loop in continuous models:

$$\forall i \in D \cup \{self\}: i \notin I_i$$

Note how one can still encode a self-loop  $(i \in I_i)$  in the internal transition function.

To translate an output event of one component (such as a departure of a customer) to a corresponding input event (such as the arrival of a customer) in influencees of that component, output-to-input translation functions  $Z_i$  are defined:

$$\{Z_{i,j} \mid i \in D \cup \{self\}, \ j \in I_i\},$$

$$Z_{self,j} : X_{self} \to X_j, \ \forall j \in D,$$

$$Z_{i,self} : Y_i \to Y_{self}, \ \forall i \in D,$$

$$Z_{i,j} : Y_i \to X_j, \ \forall i, j \in D.$$

Together,  $I_i$  and  $Z_{i,j}$  completely specify the coupling (structure and behaviour).

As a result of coupling of concurrent components, multiple state transitions may occur at the same simulation time. This is an artifact of the discrete-event abstraction and may lead to behaviour not related to real-life phenomena. A logic-based foundation to study the semantics of these artifacts was introduced by Radiya and Sargent [RS94]. In sequential simulation systems, such transition collisions are resolved by means of some form of selection of which of the components' transitions should be handled first. This corresponds to the introduction of priorities in some simulation languages. The coupled DEVS formalism explicitly represents a select function for tie-breaking between simultaneous events:

$$select: 2^D \rightarrow D$$

select chooses a unique component from any non-empty subset E of D:

$$select(E) \subset E$$

.

The subset *E* corresponds to the set of all components having a state transition simultaneously. Model coupling is the mechanism used in DEVS to group many models into a composite, coupled model. Coupled models are not distinguishable from atomic models when they are coupled with atomic models. Based on the feature of closure under coupling of DEVS, complex system can be hierarchically constructed by model coupling.

#### 1.2.2 Clarification of Concepts

#### **Sequential State and State Space Partition**

As we mentioned earlier, Sequential State is one of the key concepts used in DEVS to describe model behaviour. The Sequential State of an atomic DEVS model is the exclusive partition identifications of the model state space ([PP93]). The trajectory of the model behaviour can be seen as a sequence of numbered pairs of Sequential State and holding time, where the holding time means how long the system remains in the Sequential State. The Sequential State has different meanings depending on the model state, and it is determined by one or some of the model state variables.

A traffic light can be a good example to explain the difference between Sequential State and model state. In DEVS, a traffic light can be modelled as an atomic DEVS. The atomic traffic light DEVS model state may have many attributes such as producer, location, light colors and so forth. However, no matter how many attributes the model state may have, the life cycle of a typical traffic light can be represented as repeating changing its color to Red, Yellow, and Green after certain time intervals. So the Sequential State of a typical traffic light DEVS model can be represented as the set of {Red, Yellow, Green}. In this example, the sequential state of a traffic light is determined by the values of one attribute (light colors) of the model state.

#### External, Internal, and Output Events

There are three kinds of events for a DEVS model, Input Events (External Events), Time Scheduled Events (Internal Events), and Output Events. Input Events are events from the model's environment; Time Scheduled Events are events scheduled by the model's time advance function; and Output Events are events the model generates to communicate with its environment. Input Events cause an external state transition, so Input Events are also called External Events. Time Scheduled Events lead to an internal state transition. That is why they are also called Internal Events. Output Events are the side-effect of processing the internal events. One thing needs to be remembered is that only an internal state transition can generate Output Events. If an external transition wants to produce an Output Event, it must schedule an Internal Event, and wait until the scheduled time interval has elapsed to generate an Output Event via the scheduled Internal Event.

#### State Transition and Transition Collisions

In DEVS, State Transition means, upon the occurrence of a certain event, the behaviour that a model changes its sequential state from one to another. External events can cause an external state transition and an internal event will lead to an internal state transition. What will happen if more than one event occurs at the same simulation time? Chow presents the concept of Transition Collisions to represent mutually interfering simultaneous events ([ABK94]). Transition Collisions can happen between multiple external events, external events and internal events, and multiple internal events. Different measures to deal with Transition Collisions among simultaneous events lead to the distinction between Classic DEVS and Parallel DEVS.

With these concepts in mind, now let us discuss Parallel DEVS.

#### 1.2.3 Parallel DEVS

In Classic DEVS, the *select* function of a coupled model is used to break the tie of simultaneous internal events. At the simulation level, the simulator uses the *select* function to sequentialize these events. There is no mechanism both at atomic level and coupled model level to deal with the situations when an external event and an internal event occur simultaneously. In Classic DEVS, the external events are chosen to override any simultaneous internal event. Also, there is no mechanism for processing simultaneous external events. The simultaneous external events are simply serialized or one is selected and others are ignored.

In order to improve the capability for processing simultaneous events of Classic DEVS and to add the ability for parallel simulation, a revised version of DEVS, Parallel DEVS, was proposed. Parallel DEVS extends Classic DEVS at both atomic level and coupled level. At the atomic level, a Parallel DEVS has a input bag, which makes it possible for the Parallel DEVS to queue the distinct events happening simultaneously or the events that have not been processed yet. In

addition to the input bag, each atomic Parallel DEVS has a Confluent transition function, which is used to handle simultaneous events. Because of the existence of the Confluent transition function constructed by the modeller at the atomic level, a coupled Parallel DEVS is relieved of the burden of selecting a right event to process when there are multiple events occurring at the same time.

#### Parallel DEVS Atomic Models

The atomic model for Parallel DEVS is ([ZPK00])

APDEVS =  $(X, Y, S, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, t_a),$

where

X is the set of input events

Y is the set of output events

S is the set of sequential states

$\delta_{ext}: Q \times X^b \to S$  is the external state transition function, where  $X^b$  is a set of bags over elements in X

$\delta_{int}: S \rightarrow S$  is the internal state transition function

$\delta_{con}: S \times X^b \to S$  is the confluent transition function, subject to  $\delta_{con}(s, \emptyset) = \delta_{int}(s)$

$\lambda: S \to Y^b$  is the output function

$t_a: S \to \mathbb{R}_0^+ \cup \infty$  is the time advance function

$Q = \{(s, e) \mid s \in S, \ 0 < e < t_a(s)\}$  and e is the elapsed time since the last state transition.

Parallel DEVS improves DEVS formalism in the following areas.

- 1. The external state transition function  $\delta_{ext}$  can accept bags of input events. The major difference between the data structure set and bag is that the set is exclusively ordered, which means that an element in a set can not appear more than once. While the bag is unordered, the same element can show up many times. This improvement makes it possible for Parallel DEVS models to accept multiple events at the same time.

- 2. Parallel DEVS uses the confluent transition function  $\delta_{con}$  to deal with the transition collisions between external events and internal events. This gives the modeler an opportunity to control the model behaviour when the model receives an external event at the time of an internal state transition. The confluent transition function has two commonly used implementations, internal events first or external events first. Internal events first means, when there is a transition collision between an internal event and an external event, the internal event is processed first, then the external event. This is the default behaviour of the confluent transition function. It can be represented as  $\delta_{con}(s,x) = \delta_{ext}(\delta_{int}(s),0,x)$ . This means that the internal event is processed by the internal transition function first, immediately after that, the external event is processed by the external transition function. That is why the elapsed time is 0 for the external transition function. External events first has the opposite meaning. The confluent transition function for an exernal events first model can be described as  $\delta_{con}(s,x) = \delta_{int}(\delta_{ext}(s,t_a(s),x))$ . This means that the internal event must wait until the external event has been processed.

- 3. In Classic DEVS, external events are always processed by the external state transition function  $\delta_{ext}$ . In Parallel DEVS, an external event can be processed either by the external state transition function  $\delta_{ext}$  or by the confluent transition function  $\delta_{con}$  depending on

the time the external event arrives. When an external event arrives at a time e, if  $0 < e < t_a(s)$ , the event is processed by the  $\delta_{ext}$  function, if e = 0 or  $e = t_a(s)$ , the event is processed by the  $\delta_{con}$  function. Because the input of the confluent transition function is a bag, the implementation of the function should guarantee that  $\delta_{con}(s, \emptyset) = \delta_{int}(s)$ , which means that when the input bag is empty, the confluent transition function should have the same semantics as the internal transition function.

#### Parallel DEVS Coupled Models

The structure of a Parallel DEVS coupled model is similar to the ClassicDEVS coupled model except that the former does not have the select function ([ZPK00]).

CPDEVS =

$$\langle X, Y, D, \{M_d\}, \{I_d\}, \{Z_{i, d}\} \rangle$$

Here, X, Y, D,  $I_d$  and  $Z_{i,d}$  have the same meaning as that for Classic DEVS coupled models, and for each  $d \in D$ ,  $M_d$  is a Parallel DEVS model. For coupled models, Parallel DEVS removes the *select* function that exists in Classic DEVS coupled models. This clears the way for parallel simulation.

Now we can summarize the mechanisms used by Classic DEVS and Parallel DEVS to deal with transition collisions as follows. In Classic DEVS, transition collisions among internal events of a coupled model are tackled by the *select* function of a coupled Classic DEVS model; for transition collisions among external events and internal events, external events always override internal events; for transition collisions among external events, there is no mechanism specified in Classic DEVS to deal with this situation (which can actually never occur due to the sequential nature of Classic DEVS). In Parallel DEVS, the confluent transition function at atomic model level is used to tackle transition collisions among external events and internal events; simultaneous external events are collected in the *bag* data structure of Parallel DEVS models, and the external transition function and the confluent transition function of the Parallel DEVS accept *bags* rather than *sets* as their input parameters. Because models of Parallel DEVS are simulated in parallel, there is no transition collision among internal events.

#### 1.3 Abstract DEVS Simulation Engine

The DEVS models can be simulated in many different ways. A generic and modular framework for DEVS simulation was proposed by Zeigler in [ZPK00]. The idea of the framework is that, usually a DEVS model is a hierarchical tree in which Atomic Models as leaf nodes and Coupled Models as root and branch nodes. So the simulator of the DEVS models may have a similar hierarchical structure. In order to distinguish the difference between simulators for coupled and atomic models, the simulators for coupled models are called coordinators. The mapping between a DEVS model and its hierarchical simulator is shown below.

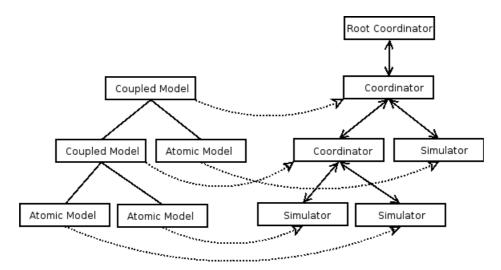

Figure 1.1: Mapping between DEVS Models and Simulators

Because it uses a sequential *select* function at coupled model level to serialize the transition collisions inside a coupled model, Classic DEVS is suitable for sequentialized simulation. On the other hand, Parallel DEVS is by nature suitable for parallel or distributed simulation. Parallel simulation can fully take advantage of the intrinsic parallelism of models. So for much complex systems, parallel simulation could be much more efficient than sequential ones. Certainly, the efficiency comes with more sophisticated algorithms, and much more effort for developing a parallel simulator.

#### 1.3.1 Abstract Simulator for Classic DEVS

The main task of a simulator is to generate a behaviour trace for the model. We mentioned earlier that there are three kinds of events in each DEVS model, external events, internal time-scheduled events, and output events. So a qualified DEVS simulator should have the capability to properly process these kinds of events. At simulation level, each DEVS event is wrapped with a time stamp, which is the virtual time at which the event occurs. In addition to the three kinds of DEVS events, the Classic DEVS simulator introduces a new type of event to synchronize the model initialization process. So there are four kinds of messages sent between DEVS simulators and coordinators. They are:

1. Initialization message (i, t): sent at the initialization time from the parent simulator object to all its subordinates;

- 2. Internal state transition message (\*, t): sent from the coordinator to its imminent child to schedule the next event;

- 3. Output message (y, t): sent from subordinates to their parents to notify output events of the subordinates;

- 4. Input message (x, t): sent from a coordinator to its subordinates to notify input events to the subordinates.

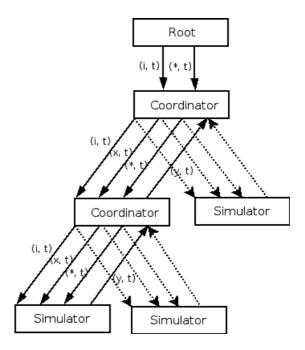

Figure 1.2: Messages Used in Classic DEVS Coordinators and Simulators

The messages sent among coordinators and simulators can be described as in Figure 1.2, in which line segments with text represent messages, and the arrow on a line segment indicates the direction of a message.

#### Simulator for Classic Atomic DEVS

From Figure 1.2, we can see that the simulator for a atomic model receives three kinds of events. At the beginning of each simulation run, the simulator receives an (i, t) event, at which the simulator updates its last event time  $t_l$  and computes its next event time  $t_n$ . Then  $t_l$  and  $t_n$  are sent to the parent coordinator.

1. A (\*, t) message can cause an internal event transition, upon which the simulator calls the model's output function to generate an output event (y, t), which is sent to the parent of the simulator. Then, the internal state transition function is called, and the model state is updated. After that the  $t_l$  and  $t_n$  variables are recomputed and sent to the parent coordinator.

- 2. When a (x, t) message is received, an external state transition is triggered. The elapsed time is computed, and the external state transition function is called. After the state transition, the  $t_l$  and  $t_n$  are updated and sent to the parent coordinator.

- 3. Every time the  $t_l$  and  $t_n$  are updated, they must be sent to the parent coordinator. By collecting all the  $t_l$ s and  $t_n$ s of its subordinates, the coordinator can determine its last and next event times. How the coordinator determines its last and next event times will be discussed in the coupled model simulation algorithm.

- 1. when an (i, t) message is received  $t_l \ = \ t \ \ e$   $t_n \ = \ t_l \ + \ t_a(s)$   $send \ t_l, \ t_n \ to \ parent$

- 2. when a (\*, t) message is received

```

if (t == t_n)

y = \lambda(s)

send (y, t) to parent

s = \delta_{int}(s)

t_l = t

t_n = t_l + t_a(s)

send t_l to parent

else

error

```

3 when a (x, t) message is received

```

\begin{aligned} &\text{if } (t_l <= t <= t_n) \\ &e = t - t_l \\ &s = \delta_{ext}(s, \, e, \, x) \\ &t_l = t \\ &t_n = t_l + t_a(s) \\ &send \, t_l, \, t_n \ to \ parent \end{aligned}  else

```

In this algorithm, variable  $t_l$  holds the virtual time when the last event occured, and the  $t_n$  represents the simulated time of the next event. During the simulation, the relation  $t_n = t_l + t_a(s)$  holds. The variable e denotes the elapsed time since the last event, at a given global time t, we have  $e = t - t_l$ . Some issues of this algorithm should be remembered. First, the internal transition will be interrupted unconditionally by an external event. There is no mechanism in this algorithm to make an external event wait until the current internal transition finishes. Second, when an internal state transition is interrupted, the unfinished internal transition is discarded. There is no way to recover the internal transition from where it is interrupted. Third, there is no provision in the algorithm for the situation when an internal transition is interrupted but the model state does not change.

#### Coordinator for Classic Coupled DEVS

As for a simulator for atomic DEVS, a coordinator for a coupled DEVS also receives three kinds of events from its parent and sends one event to its parent. The only difference is that the coordinator can also get events from its subordinates and send events to its subordinates.

- 1. When an (i, t) event is received, the coordinator forwards the (i, t) to all its direct subordinates, and collects all the subordinates' next event times and last event times, and saves them in an event list. The last and next event time for the coupled model are computed using  $t_l = max\{t_{ld} \mid d \in D\}$  and  $t_n = min\{t_{nd} \mid d \in D\}$ .

- 2. When a (\*, t) event arrives, the coordinator uses the *select* function to determine which subordinate should be executed. After the execution of the subcomponent, the coordinator updates its last time and next time.

- 3. When a (x, t) event arrives, the coordinator first checks which components are connected to the port from which the (x, t) event comes, and sends the (x, t) to the components. It then updates its last and next event time.

- 4. When receiving an output event  $(y_{d*}, t)$  from the imminent component  $d^*$ , the coordinator first checks whether the output port of  $d^*$  is connected to the coupled model. If it is, then the event will be sent to the coordinator's parent coordinator. And then, the coordinator collects the subordinates that connect with the output port of  $d^*$ , and sends  $(y_{d*}, t)$  to the subordinates.

```

1. when a (i, t) message is received

for each d in D

send (i, t) to d

get all t_{nd}s and update event-list

sort event-list according to the value of t_{nd}

t_l = max\{t_{ld} \mid d \in D\}

t_n = min\{t_{nd} \mid d \in D\}

send t_{/}, t_n to parent

2. when a (*, t) message is received

if (t == t_n)

d* = select(event-list)

send (*, t) to d*

get t_{nd*} from d* and update the event-list

sort the event-list

t_n = min\{t_{nd} \mid d \in D\}

send t_l, t_n to parent

else

error

```

```

3. when a (y_{d*}, t) message is received from port p_{d*}

if \ p_{d*} connects with one of the current coupled model's output ports

send (y_{d*}, t) to parent

for all d \in D and d has connection with p_{d*}

send (y_{d*}, t) to d

4. when a (x, t) message is received at port p

if (t_l \ll t \ll t_n)

for all d \in D and d has connection with p

send (x, t) to d through port pd that connects with p

get all tnds and update event-list

sort the event-list

t_l = t

t_n = min\{t_{nd} \mid d \in D\}

send t_l, t_n to parent

else

error

```

Here,  $t_l$  and  $t_n$  have the same meanings as that in atomic simulators. The event-list is a list of triple  $(d, t_{ld}, t_{nd})$ , and d\* means the selected component whose event will be processed next.

#### **Root Coordinator**

The root coordinator is mainly a time scheduler. There is no real DEVS model corresponding to the root coordinator. Attached to it is the real simulator that has a corresponding DEVS model. At the beginning of each simulation run, the root sends a (i, t) message to its child (the attached simulator or coordinator), and computes the next event time. Then, it repeatedly sends (\*, t) messages to its children and computes the next event time until the simulation ends.

```

t=t_0 send (i, t) to the child t=child.t_n do send (*, t) to the child t=child.t_n until simulation end condition

```

#### 1.3.2 Abstract Simulator for Parallel DEVS

The model specification for Classic DEVS in nature does not support parallel simulation. Parallel DEVS has revised the parts that impede parallel simulation of Classic DEVS models. Consequently the simulator for Parallel DEVS needs the mechanisms that support parallelism.

When it comes to parallel simulation, one important issue is how to synchronize the parallelized executions. Typically there are two different strategies used to synchronize parallel processors, conservative techniques and optimistic techniques ([AT02], [ZPK00]). The conservative method uses time stamped messages to synchronize the parallel processors. A processor is allowed to

process an event at time t, only when it is certain that no other events will arrive with a time stamp that is smaller than t. This method implies that at any time only the event with the smallest time stamp can be executed. In an optimistic parallel simulation, the processor will proceed assuming that it will not receive an event with a time stamp less than the one that is being processed. When it receives an event with a time stamp t smaller than events that have been processed, the processor will roll back the processed events to the first event whose time stamp is smaller than t.

The overhead of the conservative method is the posibly huge number of synchronization messages that are used to determine which event is the one that has smallest time stamp. In the optimistic method, in order to roll back the events, all the state information of simulation must be saved. When the system is complicated, and the state can be very large and hence the memory requirement is not a small issue.

The Parallel DEVS formalism is in nature for parallel simulation, either for the conservative method or for the optimistic approach. In the following part of this chapter, we will discuss an algorithm for conservative simulation of Parallel DEVS ([ABK94]).

As in Classic DEVS, there is a mapping structure between Parallel DEVS models and Parallel DEVS simulators. The synchronization between simulators and coordinators is also done by sending messages. In order to support the parallelism, the messages used in the Parallel DEVS simulator are slightly different from those of the Classic DEVS simulator.

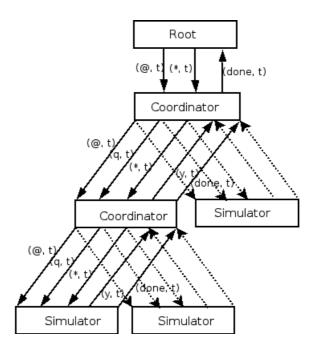

Figure 1.3: Messages for Parallel DEVS Coordinators and Simulators

Figure 1.3 shows the messages used for the implementation of a conservative Parallel DEVS simulator. There are five kinds of messages, (@, t), (q, t), (\*, t), (y, t) and (done, t). (@, t), (q,t), and (\*, t) are sent from coordinator to its subordinates, and (y, t), and (done, t) are sent by subcomponents to their parent. (@, t) is used by a coordinator to notify its subcomponents

that it is the time to generate output; (q, t) is sent by a coordinator to inform its subordinates of the arrival of an input event; and (\*, t) is to trigger the state transitions. The receiver will determine the type of the transition applied based on the context in which the message received. The (y, t) message is sent by the subordinates to their parent to notify an output; and the (done, t) is sent by a subcomponent to notify its parent that a message has been processed.

#### **Abstract Simulator for Atomic Parallel DEVS**

The main tasks of the atomic simulator are to process the received messages and report the results to the sender. The algorithm can be described as below.

```

when a (0, t) message is received

if t = t_n

y = \lambda(s)

send (y, t) to the parent coordinator

send (done, t) to the parent coordinator

else

when a (0, t) message is received

if t = t_n

y = \lambda(s)

send (y, t) to the parent coordinator

send (done, t) to the parent coordinator

else

when a (*, t) message is received

if t_l <= t <= t_n and bag is not empty

if t == t_n

if bag is empty

s = \delta_{int}(s)

else

s = \delta_{con}(s, bag)

empty bag

else

e = e - t_l

s = \delta_{ext}(s, e, bag)

empty bag

t_n = t_l + t_a(s)

send (done, t) to the parent coordinator

else

error

```

```

when a (q, t) message is received

lock the bag

add q to the bag

unlock the bag

send (done, t) to the parent coordinator

```

Rather than finishing the processing of an event in one message, this algorithm uses different messages to notify the simulator when to generate an output, process an arrived event, and when to do a state transition. This gives a clear processing structure at the cost of adding some message sending overhead. Also, the confluent function for the atomic Parallel DEVS models solves the problem of transition collision. However, an internal transition is still unconditionally interrupted when an external event occurs before the scheduled time interval for the transition elapses.

#### Coordinator for Coupled Parallel DEVS

The (@, t) message received by a coordinator is simply sent to the coordinator's subordinates. The (y, t) message is sent to all the components in the sender's influencees set  $I_i$ . If the model of the coordinator is in the  $I_i$ , then the (y, t) is sent to the coordinator's parent. For a (\*, t) message, the coordinator routes the (q, t) events down to all its atomic influencees.

```

when a (0, t) message is received from the parent coordinator

if t == t_n

t_l = t

for each child in imminent child set

send (@, t) to child

cache child reference in the synchronize set

wait until (done, t) received from all imminent children

send (done, t) to parent coordinator

else

error

when a (y, t) message is received from child i

for each influencee j in l_i

q = z_{i, j}(y)

send (q, t) to influencee j

cache j in the synchronize set

wait until (done, t) received from all influencees

if self \in I_i

y = z_{i, self}(y)

send (y, t) to the parent coordinator

when a (q, t) message received from the parent coordinator

lock the bag

add event q to the bag

unlock the bag

```

when a (\*, t) message is received from the parent coordinator

```

if t_l <= t <= t_n

for each influencee j in I_{self} and each q in bag q = z_{self,\ j}(q) send (q, t) to j cache j in the synchronize set empty bag wail until all (done, t) are received for each i in the synchronize set send (*, t) to i wait until all (done, t) are received t_l = t t_n = min\{t_i\} clear the synchronize set send (done, t) to parent coordinator else error

```

#### **Root Coordinator for Parallel DEVS**

The root coordinator has no corresponding DEVS model. It is attached to a coordinator that simulates a model. By repeatedly sending the (@, t) and (\*, t) message to the attached simulator or coordinator, the root coordinator makes the simulation run until a certain termination condition is met.

```

t = child.t_n do send (@, t) to the child wait until (done, t) received from the child send(*, t) to the child wait until (done, t) received t = child.t_n

```

until simulation end condition

There are many different ways to implement a Parallel DEVS simulator. In the next chapter, we will introduce DEVS Java and ADEVS. They both support Parallel DEVS. However, the interfaces of these two implementations are not the same.

#### 1.4 DEVS modelling and Simulation Environments

After many years of research in DEVS, there are many modelling and simulation environments for DEVS available. Here, we will give a short introduction about Python DEVS ([BV02]), DEVS Java ([Zei05]), and ADEVS([Nut05]), from which we can get a general idea of DEVS modelling and simulation. More information about the latest development of DEVS modelling and simulation environments can be found at the DEVS standardization web site <a href="http://www.sce.carleton.ca/faculty/wainer/standard/">http://www.sce.carleton.ca/faculty/wainer/standard/</a>.

#### 1.4.1 PythonDEVS

Python DEVS is a DEVS modelling and simulation package developed at MSDL (Modelling, Simulation, and Design Lab) headed by prof. Hans Vangheluwe, at McGill university. The original purpose of Python DEVS is for teaching about DEVS, so it is not very complicated. The simulator is implemented in the programming language Python, so it is called Python DEVS. From a modelling and simulation point of view, Python DEVS only supports Classic DEVS modelling and sequentialized simulation. However, with the support of the meta-modelling tool AToM<sup>3</sup>, Python DEVS has the capability of visual modelling and model transformation, which means that you can draw DEVS model visually, and transform an DEVS model to models represented in other model formalisms or vice versa. More information about Python DEVS visual modelling and model transformation can be found at <a href="http://moncs.cs.mcgill.ca/MSDL/research/projects/DEVS/">http://moncs.cs.mcgill.ca/MSDL/research/projects/DEVS/</a>.

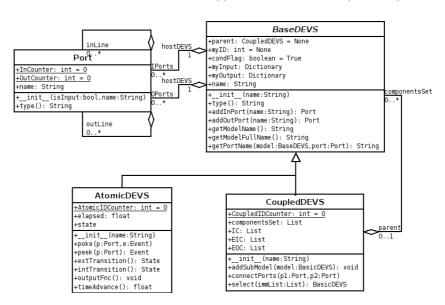

Figure 1.4: Prototypes of Python DEVS Models

Figure 1.4 is the class digram of the abstract model classes used in Python DEVS [3]. From this figure, we can see that BaseDEVS is the root of the inheritance class tree, which provides the functionalities that are common to both atomic DEVS and coupled DEVS. Besides the DEVS models, Python DEVS explicitly models a Port class. The reason for modelling the Port class is that ports cannot be neglected when you build a DEVS model especially when you want to couple models together, though ports are not explicitly described in Zeigler's DEVS specification.

The meanings of most of the attributes and the purpose of the functions are obvious. One thing that needs to be mentioned is the function of <code>getModelFullName</code>. In Python DEVS, each model instance has a name, and the name is given at the time when the model instance is created. This model name is purely a string and it can be invoked by using the function <code>getModelName</code>. After models are coupled together, the new created coupled model has a name, and the models that are coupled also have their own names. The full model name reflects the coupling relation of model names.

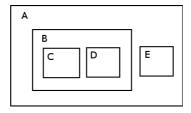

Figure 1.5: Fully Qualified Name in Python DEVS

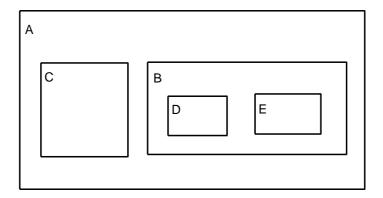

Figure 1.5 is an example of a coupled DEVS model in which model B is created by coupling models C and D, and model A is built by coupling models B and E. In this figure, C.getModelName() returns ''C" and C.getModelFullName() returns ''A.B.C". Here ''C" is the model's name and ''A.B.C" is the model's fully qualified name.

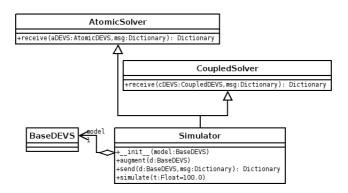

Figure 1.6: Class Diagram of the Python DEVS Simulator

Figure 1.6 shows the structure of the Python DEVS simulator. The simulator architecture is simple. Here, the AtomicSolver has the same meaning with the concept of atomic simulator we mentioned above, and CoupledSolver is an alias of the coupled coordinator mentioned earlier, and the simulator is just the root coordinator. The AtomicSolver and CoupledSolver have only one function receive. In this function, all the messages have been processed and routed to their right destinations. The purpose of the augment function in the simulator is to add time related attributes to DEVS models. This is a feature of Python, in which class instances can be augmented at run time.

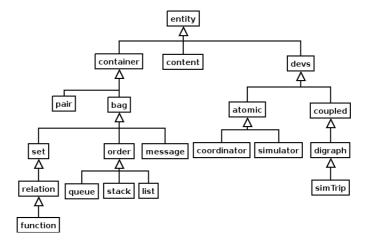

Figure 1.7: The Inheritance Diagram of DEVSJava

Figure 1.8: Class Diagram of DEVS Java

#### 1.4.2 DEVSJava

DEVSJava is a DEVS modelling and simulation environment developed by Hessam Sarjoughian and Bernard Zeigler at the University of Arizona. DEVSJava supports parallel model executions on a uni-processor. Models in DEVSJava can also be readily mapped to DEVS/HLA and DEVS/CORBA for distributed execution in combined logical/realtime settings.

Figure 1.9: Class Diagram of ADEVS

Figure 1.7 is the class inheritance diagram for DEVSJava. In this diagram we can see all

the elements in DEVSJava. Besides the classes related to DEVS, it defines some common data structures for specifying algorithms used in DEVS modelling. The simTrip on the right bottom corner of the figure plays the role of the root coordinator, which starts a simulation process.

Figure 1.8 is the class diagram for the abstract models and the simulators of DEVSJava. An interesting feature of DEVSJava is that the simulator and coordinator have the same interfaces as an atomic DEVSJava model. This means that the simulator of DEVSJava itself is modeled in DEVS!

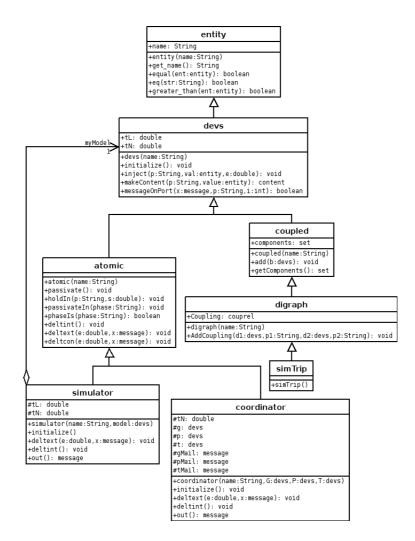

# 1.4.3 **ADEVS**

ADEVS is a DEVS modelling and simulation library developed by James J. Nutaro at the University of Arizona. ADEVS was developed in C++, and it supports both Parallel DEVS and Dynamic Structure DEVS (DSDEVS). Figure 1.9 is the class diagram of the structures of ADEVS's abstract DEVS models and simulators. These diagrams are drawn based on the source code of ADEVS at <a href="http://www.ece.arizona.edu/~nutaro/index.php">http://www.ece.arizona.edu/~nutaro/index.php</a>.

# 1.5 Conclusions

As a possible candidate for the standard of Discrete Event System modelling and simulation, DEVS provides not only specifications for building models of Discrete Event Systems, but also suggestions of building DEVS simulators. In this chapter, we first reviewed the DEVS specification. In the review, we followed the historical order of DEVS evolution, from Classic DEVS to Parallel DEVS. The major difference between Classic DEVS and Parallel DEVS is the mechanism for processing conflicting state transitions. In Classic DEVS, how to process simultaneous external events is not specified. External events have a higher priority than simultaneous internal events. Simultaneous internal events in a coupled model are processed by the order determined by the coupled model's select function. In Parallel DEVS, simultaneous external events are saved in a model's bag data structure. The conflict between simultaneous external events and internal events is resolved by the confluent function at the atomic model level. Because models are simulated in parallel at atomic model level, there is no internal state transition conflict in Parallel DEVS.

After reviewing the DEVS specification, we looked into algorithms for building DEVS simulators. Corresponding to DEVS model structure, DEVS simulator has two data structures, simulator and coordinator. Simulators provide mechanisms for simulating atomic DEVS models, whereas coordinators have facilities for simulating coupled DEVS models. The root coordinator provides time progress information to all its subordinate coordinators and simulators.

Based on the same DEVS specification, many different DEVS modelling and simulation environments have been implemented. In this chapter, we briefly introduced Python DEVS, DEVSJava, and ADEVS. Python DEVS supports Classic DEVS. DEVSJava supports Parallel DEVS. ADEVS supports both Parallel DEVS and DSDEVS. Besides the functionalities, the structures of the different implementations are also different. To show the structural differences among different implementations, we presented the class diagrams of the different implementations.

Now, we have reviewed the DEVS specification and some existing implementations. In the next few chapters, we will discuss the design and implementation of our Infrastructure of DEVS Modelling and Experimentation, the main topic of this thesis.

# Architecture and Design

# 2.1 Introduction

The reality that there are many available DEVS modelling and simulation envionments with different features significantly inhibits application of DEVS ([Zei05], [BV02], [Nut05]). Morever, due to the fact that the complex systems that need to be modelled are usually not trivial for most common users. DEVS, with its theoretical foundation, is not easy to grasp.

The main goal of this thesis research is to facilitate DEVS modelling and simulation, to promote DEVS standardization and application. The ultimate goal of DEVS modelling and simulation is to build a correct model for a system under study. The process of building a correct DEVS model usually includes the following phases, Modelling, Verification, Simulation, and Validation. So our question becomes how we can best support each step of the process.

Recently, visual modelling technology has become more and more popular in both software engineering and modelling and simulation industry. By representing models as graphs, visual modelling makes complex models easy to build, understood, and communicated. Many visual modelling languages, such as the Unified Modelling Laguange (UML, which includes both visual and textual notations), Entity Relationship Diagram(ERD), and Object Role Modelling(ORM), have been developed and applied in different domains.

DEVS is a formalism suitable for modular and hierarhical system modelling. So DEVS models are naturally represented graphically. Some beneficial research has been done on visual DEVS modelling. [PBV03] presents ideas on generating visual DEVS modelling environments using Meta-modelling technology. [PP93] proposes using Digraphs to visualize DEVS model. Though both of these have some limitations, they give helpful inspirations for visual DEVS modelling. We will enhance and improve these ideas to build a visual DEVS modelling environment to facilitate DEVS model creation and structural analysis at the Modelling stage.

When it comes to model verification, the first question is how models are represented. Some forms of representations are easy to be verified, while others are not. At present, almost in all available DEVS modelling and simulation environments, models are represented in a programming language. Models are represented in Java for DEVSJava, C++ for ADEVS, Python for Python DEVS, and so forth. Since the verification process usually needs some model structure information, programming languages are not a good choice of model representation language for verification purposes.

Modelling languages (also called model description language) are high-level declarative languages specifically designed for hight-level abstract model representation. Recently, many modelling languages have been developed and applied successfully in different industries. The Specification Description Language (SDL) has been used in telecommunication industry for de-

scribing communication protocols; UML has been used by software engineers to specify software and business models; Modelica has been used in the modelling and simulation world for specifying models of physical systems. These success stories give us some indication that representing DEVS models in a high-level modelling language is a better choice for the purpose of model verification.

High-level modelling language emphasize on specifying models in a precise and concise way. Models represented in modelling languages usually cannot be run or simulated directly. A common pratice is that in the Modelling phase, models are represented in modelling languages. When it comes to simulation, high-level modelling representations are transformed into models represented in programming languages, which are suitable for model execution or simulation. The transformation process is usually done by a model compiler. The model compiler usually at least has the following three capabilities. First, it checks whether the models are syntactically correct for a specific modelling language. Second, it verifies whether the models are structurally correct models for a certain formalism. And finally, it transforms the models to representations in a target programming language.

The model compiler can verify that a model is syntactically correct against a specific modelling language, and structurally correct against a certain modelling formalism. However, it cannot give one the confidence that the model reflects the behaviour of a real system correctly. Simulation is a process of running models with experimental data in a virtual environment to emulate the behaviour of a real system. By feeding the models with certain experimental input parameters, the virtual simulation environment can execute the models to generate output data. The output data combined with the simulation time gives the simulation trace. The behaviour of a model is reflected by the simulation trace. Comparing the simulation trace with experimental results obtained through experiments on the real system, a modeller can validate whether a model reflects the behaviour of the real system correctly.

From the discussion above, we can see that model validation is basically done by analyzing the simulation trace. In reality, the simulation trace of the models of a complex system is usually huge, so the task of model validation is not trivial. Two issues need to be considered for relieving the burden of model validation. First, representing the simulation result in an appropriate format. Second, developing tools to facilitate the validation process.