# Centro de Investigación en Ciencia Aplicada y Tecnología Avanzada

## Unidad Querétaro

# Desarrollo de un Entorno de Desarrollo Integrado (IDE) para el procesador didáctico SOPHIA

T E S I S

QUE PARA OBTENER EL GRADO DE:

MAESTRO EN TECNOLOGIA AVANZADA

PRESENTA

RAYMUNDO RAMIREZ PEDRAZA

QUERETARO, QRO.

MAYO, 2016

## INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### CARTA CESIÓN DE DERECHOS

En la Ciudad de México, D.F. el día 27 del mes de mayo del año 2016, el que suscribe Raymundo Ramírez Pedraza alumno del Programa de Maestría en Tecnología Avanzada, con número de registro B140602, adscrito al CICATA-IPN Unidad Querétaro, manifiesto que es el autor intelectual del presente trabajo de Tesis bajo la dirección del Dr. Antonio Hernández Zavala y cede los derechos del trabajo titulado "Desarrollo de un Entorno de Desarrollo Integrado (IDE) para el procesador didáctico SOPHIA", al Instituto Politécnico Nacional para su difusión, con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso expreso del autor y/o director del trabajo. Este puede ser obtenido escribiendo a las siguientes <u>direcciones: anhernandezz@ipn.mx o raymundo.r.p@gmail.com</u>. Si el permiso se otorga, el usuario deberá dar el agradecimiento correspondiente y citar la fuente del mismo.

Raymundo Ramírez Pedraza

Nombre y firma del alumno

SIP-14

# INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

## ACTA DE REVISIÓN DE TESIS

| En la Ciudad de Querétaro, Qro.  Mayo del 2016 se reunieron le por el Colegio de Profesores de Estudio para examinar la tesis titulada:  "Desarrollo de un Entorno de Desarrollo | os miembros de<br>os de Posgrado | la Comisio<br>e Investiga        | ón Revisora o<br>ción de | de la Te       | esis, d       | esign |          |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|--------------------------|----------------|---------------|-------|----------|-------|

| Presentada por el alumno:                                                                                                                                                        |                                  | 1                                |                          |                |               |       |          |       |

| Ramírez                                                                                                                                                                          | Pedraza                          |                                  |                          | Raymu          | ındo          |       |          |       |

| Apellido paterno                                                                                                                                                                 | Apellido mater                   | no                               |                          | Nombr          |               |       | -        | -     |

|                                                                                                                                                                                  | r pomoo mato                     | Con regis                        | tro: B 1                 |                |               | 6     | 0        | 2     |

| aspirante de:                                                                                                                                                                    |                                  | Conregis                         | uo. <u>B</u> 11          | - 4            | 0 1           | 0     | <u> </u> | 2     |

|                                                                                                                                                                                  |                                  |                                  |                          |                |               |       |          |       |

| Maestría en Tecnología Avanzada                                                                                                                                                  |                                  |                                  |                          |                |               |       |          |       |

| Después de intercambiar opiniones, los                                                                                                                                           | s miembros de                    | la Comisió                       | n manifesta              | ron <i>API</i> | ROBA          | AR LA | 4 TE     | :SIS, |

| en virtud de que satisface los requisitos                                                                                                                                        | senalados por l                  | as disposi                       | ciones regiar            | nentaria       | as vige       | entes |          |       |

| LA                                                                                                                                                                               | COMISIÓN R                       | EVISOR                           | Δ                        |                |               |       |          |       |

| _                                                                                                                                                                                |                                  |                                  | •                        |                |               |       |          |       |

|                                                                                                                                                                                  | Director(a) d                    | e tesis                          |                          |                |               |       |          |       |

|                                                                                                                                                                                  |                                  | _                                |                          |                |               |       |          |       |

|                                                                                                                                                                                  |                                  |                                  |                          |                |               |       |          |       |

|                                                                                                                                                                                  | Date Stands                      | don Toursto                      |                          |                |               |       |          |       |

| ·                                                                                                                                                                                | DF Abrobio Hernan                | dez Zavala                       |                          |                |               |       |          |       |

| 7                                                                                                                                                                                |                                  |                                  | 11.                      | $+_{1}$        |               |       |          |       |

| Ment                                                                                                                                                                             |                                  |                                  | llu                      | المعاير        | _             |       |          |       |

| <i>UDM</i>                                                                                                                                                                       |                                  |                                  | 1                        |                | $\mathcal{I}$ |       |          |       |

| Dr. Juan Bautista Hurtado Ramos                                                                                                                                                  |                                  |                                  | Dr. Jorgé Adelbe         | rto Huerta     | Ruelas        |       |          |       |

| Januar 60                                                                                                                                                                        |                                  |                                  | · A                      | 1              | l             |       |          |       |

| Taglos ! e                                                                                                                                                                       |                                  |                                  | ( )                      | 90/2/          |               |       |          |       |

| Dr. José Joel González Barbosa                                                                                                                                                   |                                  | E EDUCAC                         | Dr. Julio Cesai          | Sosa Sav       | vedra         |       |          |       |

| PRESIDENT                                                                                                                                                                        | - DEL 001 E                      | Later St.                        | .==-                     | A              |               |       |          |       |

| PRESIDENT                                                                                                                                                                        | E DEL COLEG                      | OPERRO                           | DFESORES                 |                |               |       |          |       |

|                                                                                                                                                                                  | a sign                           | WEXICO<br>WEXICO                 |                          |                |               |       |          |       |

|                                                                                                                                                                                  | J. J. J.                         | OLITÉCNICO NA<br>LE INVESTIGACIÓ | CIONAL<br>IN EN          |                |               |       |          |       |

|                                                                                                                                                                                  |                                  | NCM APLICADA<br>Z dassovanza     | DA .                     |                |               |       |          |       |

|                                                                                                                                                                                  |                                  | RECCIÓN                          | I                        |                |               |       | ,        |       |

## **DEDICATORIA**

A Dios por haberme puesto en este camino.

A mi mamá porque sin ella no estaría aquí.

A mi hermana por siempre estar a mi lado para apoyarme.

A mi hermano por ser un ejemplo a seguir

## **AGRADECIMIENTOS**

A CONACYT por el apoyo otorgado durante mi estancia en CICATA-QRO.

Al Centro de Investigación en Computación (CIC-IPN) y los doctores que me recibieron en mi estancia en su Centro de Investigación.

A la Dra. Eva González Jasso, directora de este Centro de Investigación por el apoyo brindado durante mi estancia en la maestría.

Al Dr. Antonio Hernandez Zavala por la confianza y apoyo recibido durante el desarrollo del proyecto.

A los miembros de mi cómite por su apoyo, asesoria y consejos que me han ayudado a crecer en todos los ambitos.

A mis amigos de la preparatoria y universidad que pese a la distancia siempre han estado presentes. Y por supuesto a los amistades que se han hecho durante la maestría: Silvia, Rodrigo, Julian y Martin, gracias por estar en mí día a día, por el apoyo y los buenos momentos que se han pasado y por los estoy seguro que vendrán.

## RESUMEN

A nivel mundial dentro del área de computación en los cursos de arquitectura de computadoras los recursos didácticos utilizados no favorecen la correcta y completa asimilación de los conceptos. Algunas universidades desarrollan sus propios recursos (principalmente simuladores y hardware), desarrollados, cada alumno cuenta con su propia herramienta; en cambio en los cursos que se imparten en las instituciones mexicanas, no se cuenta con una herramienta adecuada para facilitar la comprensión de la estructura interna de una computadora. Por esa razón fue diseñado el procesador con fines didácticos llamado SOPHIA, que ayuda a mostrar cómo se comunican los bloques funcionales del procesador. Para hacer uso de este, se tiene que programar en lenguaje máquina. De esta manera existe la necesidad de una herramienta que facilite la interacción con el procesador, en este proyecto se propone el desarrollo de un compilador para el procesador SOPHIA; con la finalidad de contar con una herramienta didáctica amigable y con los resultados obtenidos en el desarrollo del compilador, también se desarrollo un simulador, obteniendo como resultado un Entorno de Desarrollo Integrado (IDE, por sus siglas en inglés, Integrated Development Environment), que facilita la abstracción de los conceptos del curso de arquitectura de computadoras.

## **ABSTRACT**

Worldwide within the area of computing, specify in computer architecture courses there aren't many teaching tools to be used. The few tools that exist don't help to the correct and complete assimilation of concepts. Some Universities develop their own resources (mainly simulators and hardware). In developed countries, each student has their own tool. In other hand, Mexican institutions there aren't a suitable tool to facilitate understanding of the internal structure of a computer. For that reason the processor SOPHIA was develoed for teaching purposes, which helps to show how the functional blocks of the processor communicate between their. However, to can use this, you must be programmed in machine language (0, 1). Thus there is a need for a tool to facilitate interaction with the processor, in this project is proposed the development of a compiler for the processor SOPHIA; in order to have a friendly educational tool that facilitates abstraction of the concepts of computer architecture course and in base the results obtained in the development of the compiler, also was developed a simulator; getting a IDE (Integrated Development Environment). This didactic tool helps in abstracting the concepts of computer architecture course.

# **ÍNDICE GENERAL**

| Índice de figuras                                    | IX  |

|------------------------------------------------------|-----|

| Índice de tablas                                     | XII |

| Capítulo 1 Introducción                              | 1   |

| 1.1 Descripción del problema                         | 2   |

| 1.2 Justificación                                    | 3   |

| 1.3 Objetivo general                                 | 3   |

| 1.4 Objetivos específicos                            | 4   |

| 1.5 Estructura de la tesis                           | 4   |

| Capítulo 2. Estado del arte                          | 5   |

| 2.1 Procesadores didácticos                          | 8   |

| 2.2 Compiladores y herramientas de desarrollo        | 19  |

| 2.3 Entorno de desarrollo integrado                  | 23  |

| Capítulo 3. Marco teórico                            | 26  |

| 3.1 Procesador didáctico sophia                      | 26  |

| 3.1.1 Carácteristicas y arquitectura                 | 26  |

| 3.1.2 Conjunto de instrucciones                      | 28  |

| 3.1.3 Modos de direccionamiento                      | 28  |

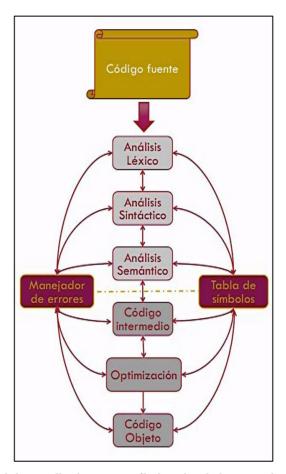

| 3.2 Compiladores                                     | 34  |

| 3.2.1 Análisis léxico                                | 37  |

| 3.2.1.1 Tabla de transiciones                        | 41  |

| 3.2.2 Análisis sintáctico                            | 44  |

| 3.2.2.1 Forma normal de chomsky                      | 49  |

| 3.2.2.2 Principio del preanálisis                    | 51  |

| 3.2.2.3 Forma normal de backus                       | 53  |

| 3.2.3 Análisis semántico                             | 54  |

| 3.2.4 Generación y optimización de código intermedio | 55  |

| 3.2.5 Generación de código máquina                   | 56  |

| 3.2.6 Manejador de errores                           | 56  |

| 3.2.7 Tabla de simbolos                              | 58  |

| 3.3 Simulador                                        | 59  |

| Capítulo 4. Entorno de desarrollo integrado          | 60  |

| Capítulo 5. Experimentación y resultados             | 72  |

| Capítulo 6. Conclusión | 78 |

|------------------------|----|

| Trabajo futuro         | 78 |

| Referencias:           | 79 |

# **ÍNDICE DE FIGURAS**

| Figura 3. 1 Arquitectura del procesador SOPHIA.                            | 27          |

|----------------------------------------------------------------------------|-------------|

| Figura 3. 2 Direccionamiento directo a memoria, donde el código de op-     | eración     |

| define el tipo de slto y dato constante el nímero de la próxima instru     | ucción a    |

| ejecutar                                                                   | 28          |

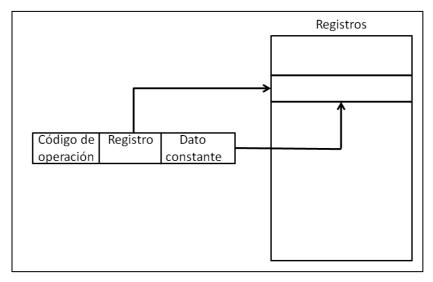

| Figura 3. 3 Direccionamiento instrucciones inmediatas, el dato constant    | e actualiza |

| el valor del registro                                                      | 31          |

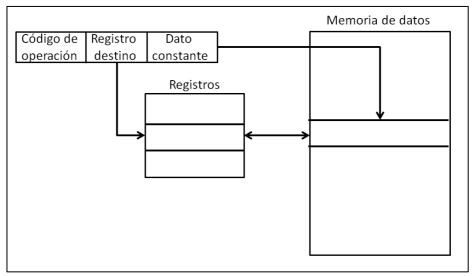

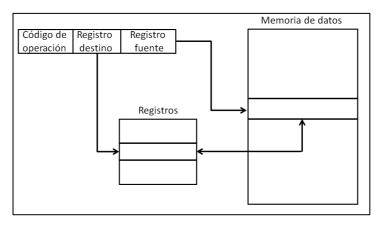

| Figura 3. 4 Direccionamiento dato directo desde memoria de datos, el c     | lato        |

| constante determina la localidad de memoria la memoria de datos            | a la que se |

| accederá para obtener su valor, mismo que ha de ser cargado en e           | el registro |

| destino                                                                    | 31          |

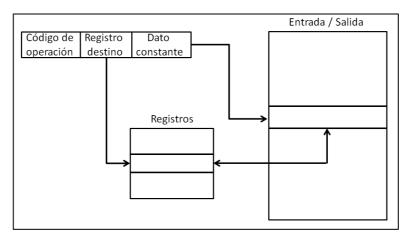

| Figura 3. 5 Direccionamiento de Entrada/Salida, el dato constante deter    | rmina la    |

| localidad de memoria la memoria de datos a la que se almacenará            | el valor    |

| del registro                                                               | 32          |

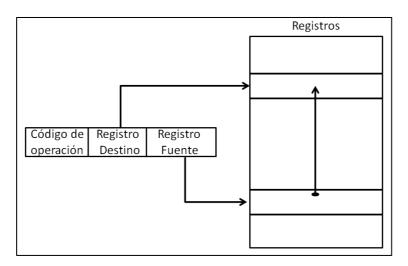

| Figura 3. 6 Direccionamiento directo con dos registros, el valor del regis | stro fuente |

| es almacenado en el registro destino                                       | 32          |

| Figura 3. 7 Direccionamiento acceso indirecto a memoria mediante un i      | registro,   |

| registro fuente es un apuntador a memoria de datos, el código de d         | peración    |

| define si se lee o escribe el valor de la memoria de datos en el regi      | stro        |

| destino                                                                    | 33          |

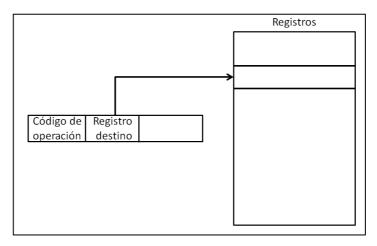

| Figura 3. 8 Direccionamiento acceso directo un solo registro, el resultad  | do de la    |

| ALU es almacenado en el registro destino                                   | 33          |

| Figura 3. 9 Etapas para el desarrollo de un compilador, donde la etapa     | de análisis |

| esta compuesto por: analizador léxico, sintáctico y semántico y la e       | etapa de    |

| síntesis lo compone la generación de codigo intermedio, su optimiz         | zación y la |

| obtención de código objeto                                                 | 36          |

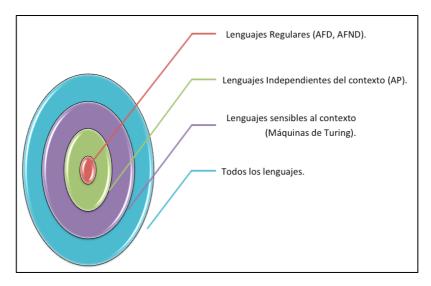

| Figura 3. 10 Clasificación de los diferentes lenguajes determinada por 0   | Chomsky.    |

|                                                                            | 37          |

| Figura 3. 11 Gramática que produce frases complejas y completas en e       | l lenguaje  |

| español                                                                    | 38          |

| Figura 3. 12 Gramática regular correspondiente al lenguaje                 |             |

| L(G)={ x <sup>m</sup> y <sup>n</sup> : m, n ε N}                           | 40          |

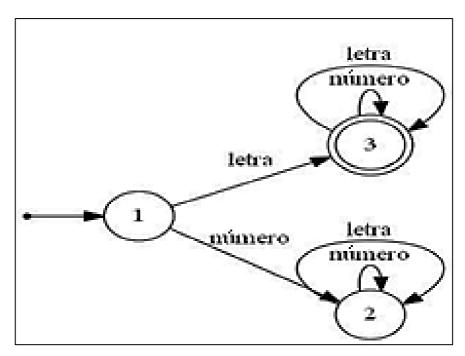

| Figura 3. 13 Autómata finito que reconoce identificadores válidos         | 41           |

|---------------------------------------------------------------------------|--------------|

| Figura 3. 14 Algoritmo general para generar un autómata finito determi    | nista que    |

| acepte identificadores válidos                                            | 42           |

| Figura 3. 15 Algoritmo del autómata finito que reconoce identificadores   | válidos43    |

| Figura 3. 16 Estructura de las instrucciones Si, Si-SiNo                  | 45           |

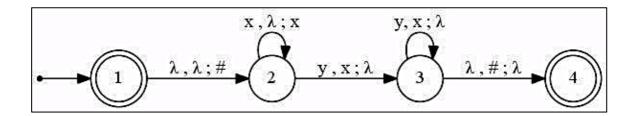

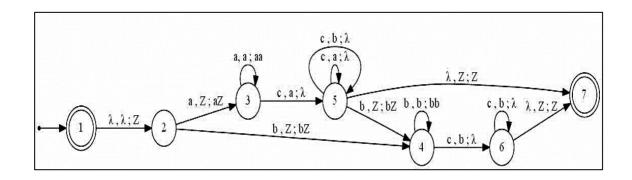

| Figura 3. 17 Autómata de pila que reconoce la expresión (xy)*             | 46           |

| Figura 3. 18 Autómata de pila que reconoce cadenas palíndromas de lo      | ongitud par. |

|                                                                           | 47           |

| Figura 3. 19 Gramática que produce la expresión (xy)*                     | 49           |

| Figura 3. 20 Algoritmo que convierte una GIC a una GFNC                   | 50           |

| Figura 3. 21 Algoritmo para realizar un analizador sintáctico LL(k)       | 52           |

| Figura 3. 22 Algoritmo para realizar un analizador sintáctico LR(k)       | 53           |

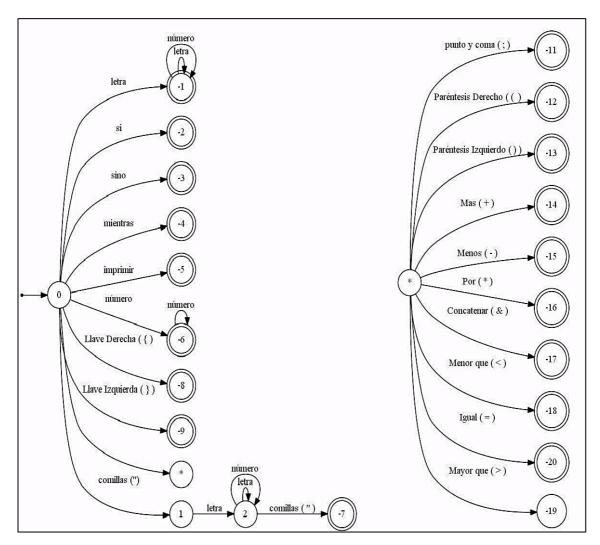

| Figura 4. 1 Expresiones regulares utilizadas para generar el analizador   | ·léxico 60   |

| Figura 4. 2 Autómata finito determinista correspondiente al análisis léxi |              |

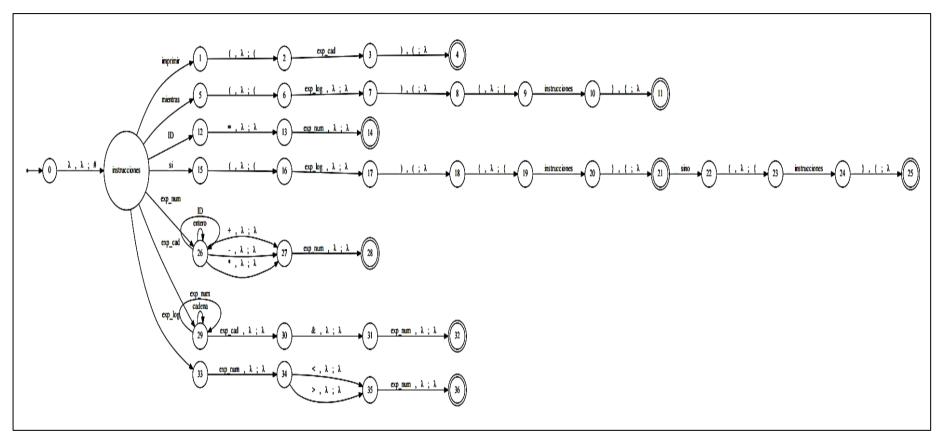

| Figura 4. 3 a) Gramática BNF instrucciones de control del compilador      |              |

| Figura 4. 4 Analizador sintáctico mediante un autómata de pila            |              |

| Figura 4. 5 Fragmento de código correspondiente a la generación de co     |              |

| intermedio                                                                | _            |

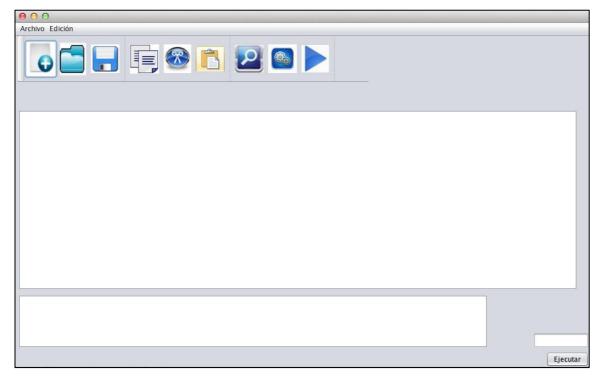

| Figura 4. 6 Interfaz del compilador                                       |              |

| Figura 4. 7 Botón que permite crear un nuevo programa                     |              |

| Figura 4. 8 Botón que permite abrir un programa ya existente              |              |

| Figura 4. 9 Botón que permite guardar el código escrito en el área de tr  |              |

| Figura 4. 10a) Botón que permite copiar el texto seleccionado             | •            |

| Figura 4. 11 Botón que permite cortar el texto seleccionado               |              |

| Figura 4. 12 Botón que pegar el texto que se haya copiado o cortado       |              |

| previamente                                                               | 69           |

| Figura 4. 13 Botón compilar                                               |              |

| Figura 4. 14 Botón ejecutar                                               |              |

| Figura 4. 15 Botón simular                                                |              |

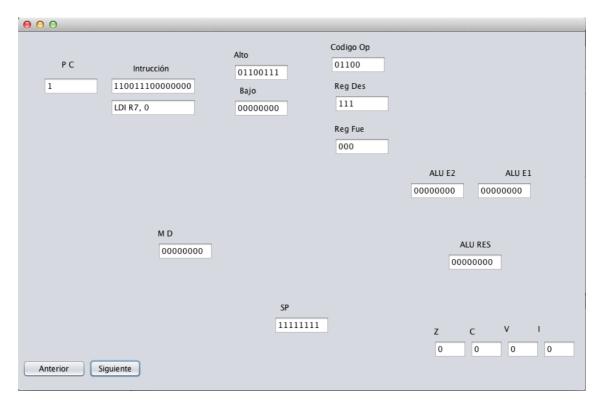

| Figura 4. 16 Interfaz del simulador                                       |              |

| Figura 5. 1 a) Código error imprimir y declaración de variable. b) Menseajes de     |

|-------------------------------------------------------------------------------------|

| errores72                                                                           |

| Figura 5. 2 a) Código error mientras y declaración de variable por falta de ";". b) |

| Menseajes de errores73                                                              |

| Figura 5. 3 a) Código error símbolo no identificado. b) Menseajes de errores74      |

| Figura 5. 4 a) Código error falta de símbolo de concatenación. b) Menseajes de      |

| errores74                                                                           |

| Figura 5. 5 a) Código error falta de token aritmético. b) Menseajes de errores75    |

| Figura 5. 6 a) Ejecución de código sin errores. b) Resultado de la ejecución de     |

| código sin errores76                                                                |

| Figura 5. 7 a) Ejecución del simulador77                                            |

## **ÍNDICE DE TABLAS**

| Tabla 2. 1 Metodos de ensenanza utilizados en cursos de arquitectura de           |

|-----------------------------------------------------------------------------------|

| computadoras7                                                                     |

| Tabla 2. 2 Procesadores didácticos desarrollados en universidades a nivel         |

| mundial9                                                                          |

|                                                                                   |

| Tabla 3. 1 Conjunto de instrucciones del procesador SOPHIA29                      |

| Tabla 3. 2 Tabla de transiciones correspondiente al autómata de la Figura 3.13.43 |

| Tabla 3. 3 Traducción de una instrucción de alto nivel a lenguaje ensamblador55   |

| Tabla 3. 4 Tabla de símbolos del compilador58                                     |

|                                                                                   |

| Tabla 4. 1 Traducción de una asignación simple en alto nivel a lenguaje           |

| ensamblador65                                                                     |

| Tabla 4. 2 Traducción de una instrucción de alto nivel a lenguaje ensamblador66   |

| Tabla 4. 3 Descripción del uso de los registros del procesador SOPHIA67           |

| Tabla 4. 4 Código máquina generado correspondiente a una asignación de una        |

| suma a una variable67                                                             |

# **CAPÍTULO 1 INTRODUCCIÓN**

Hoy en día las computadoras son una herramienta utilizada para realizar cualquier tipo de cálculos en casi cualquier área: como en el sector de telecomunicaciones, las finanzas, el ramo automotriz, los sistemas de control, entre otras.

Existen diferentes tipos de computadoras, cuya principal diferencia es la cantidad de información que puede procesar. Debido a que la información es agrupada en paquetes de 8 bits, existen procesadores de 8, 16, 32, y 64 bits. Siendo estos dos últimos los más comunes, pues se encuentran en las computadoras de escritorio, laptop, notebook, tabletas, o cualquier otra computadora personal. Las computadoras de 16-bits son usadas comúnmente en el área de las telecomunicaciones y aplicaciones industriales.

A pesar de que la mayoría de las personas no conoce la existencia de procesadores de 8 bits, son los procesadores más vendidos en el mundo, debido a que estos pueden ser usadas como controladores de tareas computacionales sencillas. Entonces se puede puntualizar, las computadoras más simples son aquellas que poseen los procesadores de 8-bits.

Por la necesidad de contar con una herramienta didáctica para los cursos de arquitectura de computadoras se desarrolló el procesador SOPHIA. El procesador posee un bus de datos de 8 bits y un conjunto reducido de instrucciones (*RISC*). Incluye un conjunto de instrucciones consistentes y todos los bloques funcionales, tales como *memoria de datos* y *memoria de programa*, una *unidad lógica aritmética* sencilla (*ALU*) para operaciones básicas. Su modo de funcionamiento es la ejecución multiciclo dada su facilidad de visualización.

El procesador SOPHIA se implementó en un *FPGA* de *Xilinx Spartan-3E* para ser una biblioteca (softcore) que se puede usar como herramienta didáctica en los cursos de arquitectura de computadoras, cuya intención principal es proporcionar a los estudiantes una herramienta flexible pero consistente para la comprensión de arquitectura de computadoras desde sus fundamentos, siendo la base para resolver cualquier tipo de problemas didácticos dentro de los cursos de arquitectura de computadoras, como los pueden ser: realizar actividades prácticas donde se identifiquen y manejen componentes de hardware y comprender su funcionamiento, mediante la formalización de conceptos a través de la observación y reflexión para la posterior resolución de problemas. Este procesador está basado en la arquitectura *Harvard* que consiste en separar la memoria necesaria para el programa y otra más para almacenamiento de datos.

Todo hardware requiere de un software para funcionar. Debido a que ya se cuenta con el procesador (hardware) entonces, en el presente trabajo se realizará el desarrollo de un Entorno de Desarrollo Integrado IDE (software) mismo que será utilizado como interfaz entre el usuario y el procesador, permitiendo el desarrollo de programas y haciendo uso del conjunto de instrucciones que contiene el procesador. Para que sea posible desarrollar este IDE es necesario conocer la arquitectura de la computadora con la que se va a trabajar, las etapas que se deben tomar en cuenta y los recursos que se necesitan para la ejecución de los programas.

### 1.1 DESCRIPCIÓN DEL PROBLEMA

A nivel mundial dentro del área de computación en los cursos de arquitectura de computadoras los recursos didácticos utilizados no favorecen la correcta y completa asimilación de los conceptos, siendo estos la base para la transversalidad que existe con algunos otros cursos. Ha habido universidades que desarrollaron sus propios recursos (principalmente simuladores y hardware) para ser implementados en asignaturas de la misma universidad, en países desarrollados hay suficiente presupuesto para proporcionar a cada alumno su simulador y/o hardware para la comprensión de los conceptos a través de llevarlos a la práctica.

En cambio en los cursos de arquitectura de computadoras que se imparten en las instituciones de nivel superior en México, no se cuenta con una herramienta adecuada para facilitar la comprensión de la estructura interna de una computadora, porque no se enseña la fabricación de circuitos integrados, pues en ocasiones no se cuenta con las herramientas adecuadas para hacerlo a diferencia de países desarrollados o simplemente no es una prioridad, llevando a utilizar métodos como el papel. Es por esto que existe la necesidad de desarrollar tecnología propia.

Por esta razón se desarrolló el procesador SOPHIA, el cual busca que los alumnos tengan una mayor comprensión del funcionamiento interno de una computadora.

#### 1.2 JUSTIFICACIÓN

Debido a que en la actualidad existen pocas herramientas prácticas para ayudar a los estudiantes a asimilar mejor los conocimientos de los cursos de arquitectura de computadoras, en el presente trabajo se desarrollará un IDE (Entorno de Desarrollo Integrado) que servirá como intermediario entre el usuario y la computadora para que el procesador didáctico SOPHIA sea una herramienta práctica en cursos de arquitectura de computadoras.

#### **1.3 OBJETIVO GENERAL**

Desarrollar un Entorno de Desarrollo Integrado para que el procesador SOPHIA pueda ser usado como herramienta didáctica por los alumnos de los cursos de arquitectura de computadoras a nivel superior y posgrado.

## 1.4 OBJETIVOS ESPECÍFICOS

- Definir los elementos léxicos, la estructura del programa y el diccionario de datos.

- Realizar y validar la fase de análisis del compilador para informar al usuario sobre los posibles errores, así como su tipo y ubicación.

- Realizar y validar la fase de síntesis del compilador para generar el código máquina.

- Implementar el IDE y validar su funcionamiento.

#### 1.5 ESTRUCTURA DE LA TESIS

En el capítulo 2 se presenta el estado del arte respecto al trabajo que ha sido realizado del desarrollo de procesadores con fines didácticos, así como de compiladores y herramientas de desarrollo para los mismos y la creación de entornos de desarrollo integrado. En el capítulo 3 se describe el marco teórico donde se presenta la teoría de autómatas y lenguajes formales, basados en la jerarquía de Chomsky y el principio del preanálisis. En el capítulo 4 se muestra el desarrollo del IDE para el procesador SOPHIA. En el capítulo 5 se dan a conocer las pruebas y resultados. Finalmente en el capítulo 6 se presenta la conclusión y se da una descripción del trabajo futuro.

## **CAPÍTULO 2. ESTADO DEL ARTE**

En 1950 fue desarrollada la primera computadora de 2 bits por Edmund Berkeley y Robert Jensen, representando esto la punta de lanza para que el desarrollo de procesadores educativos y métodos de enseñanza fueran estudiados para explicar arquitectura de computadoras y asegurar la comprensión de las funciones de cada uno de sus bloques funcionales (partes que lo conforman) [1].

Los diferentes métodos de enseñanza que se han desarrollado desde 1950, se pueden clasificar en 5 categorías debido a su naturaleza y a las necesidades que se tienen, entender cada uno de sus bloques funcionales, el desarrollo de un procesador, la transferencia entre sus bloques, a continuación se muestran las 5 categorías de los métodos didácticos y las diferentes aplicaciones que se desarrollaron para cada una de ellas:

- 1.-Papel: El Dr. Stuart Madnick diseñó la "Little Man Computer LMC" en 1965 [2], para enseñar a sus estudiantes. Otro enfoque de esta técnica, es la computadora "CARDIAC" desarrollado por David Hagelbarger y Saúl Fingerman de los Laboratorios Bell en 1968 [3], es un procesador que en la actualidad se implementa en un software simulador. Por último, el "Paper Processor", desarrollado por Saito Yutaka en 2010 [4]. Estas aplicaciones se han tomado como base para desarrollar versiones modernas sin perder la esencia de mostrar las características básicas de las computadoras, entender su funcionamiento, pero sin dejar de lado la programación de las mismas.

- 2.- Hardware: En este enfoque es común el uso de componentes digitales MSI tales como TTL para construir un equipo como Glen G. Langdon en 1982[5]; procesador "SC-16" de 16 bits [6]; el procesador "DLX" de 32 bits desarrollado por Hennessy-Patterson en 1990 [7]. El procesador de 16 bits "PISC" de Bradford Rodríguez en 1994 [8]. En los cursos de arquitectura de computadoras es usado este enfoque para sincronizar la transferencia de datos entre los bloques funcionales.

- **3.- Simulador:** Existen diversas herramientas de simulación que se enfocan a la enseñanza de arquitectura de computadoras [9]–[15], estas permiten la ejecución de un código y se tiene como resultado la visualización de la transferencia de datos entre los bloques funcionales del procesador de forma gráfica.

- 4.- Lenguajes de descripción de Hardware (HDL): Se han desarrollado muchos tipos de procesadores didácticos para este enfoque, existen versiones de 8, 16 y 32 bits [16]–[22]. Esta opción permite la construcción física de una computadora simple mediante el uso de dispositivos FPGA programados por un HDL. La principal ventaja es que el tiempo requerido para desarrollar un procesador es bastante corto, pero la principal desventaja es la falta de comprensión en el flujo de datos inducida por la programación.

- 5.- Bloques lógicos: Este enfoque permite a los estudiantes comprender plenamente un procesador a partir de sus fundamentos, mediante la integración y la sincronización de sus bloques funcionales. Varios autores prefieren este método para sus cursos [19], [23]–[28], pues consideran que esta es la mejor opción de desarrollo, permitiendo la creación de cada bloque funcional para probarlo y lograr una mejor integración [29].

En la Tabla 2.1 se muestran los métodos de enseñanza en los cursos de arquitectura de computadoras donde se muestra una pequeña descripción de cada uno de ellos, sus ventajas y desventajas.

Tabla 2. 1 Métodos de enseñanza utilizados en cursos de arquitectura de computadoras.

| Método                                  | Descripción                                                                             | Ventajas                                                                                                                                          | Desventajas                                                                                                 |

|-----------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Papel                                   | Primera técnica<br>utilizada.                                                           | Costo, simpleza.                                                                                                                                  | No se podía entender<br>el verdadero<br>propósito de una<br>computadora.                                    |

| Hardware                                | Este tipo de equipo se construye utilizando cualquier tecnología existente.             | Sincronizar la<br>transferencia de<br>datos entre los<br>bloques funcionales.                                                                     | El tiempo invertido en el cableado.                                                                         |

| Simulador                               | Permite la ejecución<br>de un código para ver<br>la funcionalidad de la<br>computadora. | La mayoría de estos<br>son entornos<br>gráficos, se pueden<br>ver todos los bloques<br>funcionales y la<br>transferencia de<br>datos entre ellos. | Sólo permite ver el<br>funcionamiento<br>completo del<br>procesador, no así de<br>cada unidad<br>funcional. |

| Lenguajes<br>de<br>descripción<br>(HDL) | Permite la construcción física de una computadora simple.                               | Tiempo de desarrollo corto.                                                                                                                       | Falta de comprensión<br>en el flujo de datos.                                                               |

| Bloques<br>lógicos.                     | Diseñado para<br>dispositivos de lógica<br>programable de cada<br>unidad funcional.     | Permite a los estudiantes comprender plenamente un procesador a partir de sus fundamentos.                                                        | Tiempo de diseño.                                                                                           |

## 2.1 PROCESADORES DIDÁCTICOS

Al utilizar el término *procesador didáctico* se hace referencia tanto a la flexibilidad del procesador para emular máquinas sencillas, como a su capacidad para permitir la observación y/o modificación de su estado interno. El objetivo es facilitar la comprensión en cursos de arquitectura de computadoras mediante material didáctico, que pueda apoyar la enseñanza del funcionamiento detallado del hardware para no limitarse a la teoría, permitiendo ejemplificar los nuevos métodos de diseño de sistemas digitales basados en el uso de lenguajes de descripción de hardware (*HDLs*). Teniendo el código fuente HDL sintetizable abre la posibilidad de utilizar microprocesadores sencillos que pueden ser analizados o diseñados por el estudiante para poder comprender mejor su funcionamiento.

El principal propósito de los procesadores didácticos debe ser mostrar cómo está diseñada una computadora y como se pueden vincular sus componentes mediante la transferencia de información. También deben ser capaces de permitir a los estudiantes desarrollar y probar sus propios microprogramas (pueden ser programados en alto nivel, ensamblador o lenguaje máquina) mediante la ejecución y simulación de los mismos para comprobar que el programa realiza la tarea para el cual fue desarrollado.

En la Tabla 2.2 se puden observar las principales características de los procesadores didácticos que se han desarrollado en universidades a nivel mundial.

Tabla 2. 2 Procesadores didácticos desarrollados en universidades a nivel mundial.

|                        | Arquitectura | Set de instrucciones | Bits de datos | Registro de<br>Propósito General | Numero de instrucciones | Memoria de<br>datos | Memoria de<br>programa |

|------------------------|--------------|----------------------|---------------|----------------------------------|-------------------------|---------------------|------------------------|

| SOPHIA [2]             | Harvard      | RISC                 | 8-bits        | 8                                | 29, 16/24-bit           | 256 x 8-bit         | 256 x 16-bit           |

| MMP16 [4]              | Von Neumann  | ISA                  | 16 bits       | 16                               | 35, 16/32-bit           |                     | 16K x 16-bit           |

| ESCOMIPS [5]           | Harvard      | RISC                 | 16 bits       | 16                               | 16, 25-bit              | 64k x 16-bit        | 64k x 25-bit           |

| *BIP I <sup>[6]</sup>  | Harvard      | RISC                 | 16-bits       | 25                               | 8, 16-bit               | 1K x 16-bit         | 1K x 16-bit            |

| *BIP II <sup>[6]</sup> | Harvard      | RISC                 | 16-bits       | 25                               | 15, 16 bit              | 1K x 16-bit         | 1K x 16-bit            |

| MIC-1 [7]              | Von Neumann  | CISC                 | 16-bits       | 16                               | 32, 16-bit              |                     | 16-bit                 |

| SWEET-16 [8]           | Harvard      | RISC                 | 16-bits       | 8                                | 16, 8 bit               | 16-bit              | 16-bit                 |

| MPD <sup>[9]</sup>     | Von Neumann  | CISC                 | 8-bits        | 7                                | 18, 8-bit               | 256 x 8-bits        | 256 x 8-bits           |

|                         | Arquitectura | Set de instrucciones | Bits de datos | Registro de<br>Propósito General | Numero de instrucciones | Memoria de<br>datos | Memoria de<br>programa |

|-------------------------|--------------|----------------------|---------------|----------------------------------|-------------------------|---------------------|------------------------|

| NEANDER [10]            | Von Neumann  | ASIC                 | 4-bits        |                                  | 8                       |                     | 256 x 4-bit            |

| NEANDER [11]            | Von Neumann  | CISC                 | 8-bits        |                                  | 9                       |                     | 256 x 8-bit            |

| ANEM [39]               | Harvard      | RISC                 | 16-bits       | 16                               | 21                      | 64k x 16-bit        | 64k x 16-bit           |

| ILA9200 <sup>[13]</sup> | Harvard      | ASIC                 | 16-bits       | 20                               |                         | 16-bit              | 16-bit                 |

| CABARE [14]             | Von Neumann  | RISP                 | 32-bit        | 11                               | 20                      |                     | 8k x 32-bit            |

| TINYCPU [15]            | Harvard      | RISC                 | 16-bits       |                                  | 29                      | 16-bit              | 256k x 16-bit          |

Desde que se inició el estudio de procesadores didácticos, ha habido el desarrollo de varios procesadores para dicho fin, como el Microprocesador didáctico microprogramado de 16-bit (*MMP16*), el cual se desarrolló como una herramienta de estudio mediante el uso de los componentes electrónico-digitales y la implementación total de un microprocesador digital.

*MMP16* está enfocado principalmente a la educación, posee una unidad de control, y una unidad de procesamiento de datos, este procesador usa dos diferentes señales de reloj (una para ser usado por la *unidad de control* y definir los estados de la máquina; y el segundo para cargar los registros de la *unidad de procesamiento* de datos y sincronizar las señales de memoria y buses), una arquitectura Von Neumann de 16-bit, Memoria de 16-bit, 16 registros de propósito general, conjunto de instrucciones reducidas y 35 instrucciones (16 / 32 bit) [25].

Por otra parte, los sistemas integrados han venido incrementando su potencial, tanto de procesamiento como de integración en un mismo chip, para poder dar paso a sistemas más complejos. De esta manera es posible utilizar un procesador concreto o hacer uso de la lógica programable, dando paso a los **System on a Programmable Chip** (**SoPC**) que permiten implementar en un único dispositivo sistemas complejos que antes empleaban varios circuitos integrados en un mismo circuito integrado. Al emplear un **FPGA** se tiene la ventaja de poder emplearse para el prototipado de un **ASIC** o bien ser un sistema final. Además se cuenta con la capacidad de expandir el sistema en caso de ser necesario.

Muchos procesadores han adquirido esta arquitectura por ser una de las más eficientes. Los *Microprocessor without Interlocked Pipeline Stages* (*MIPS*) son utilizados en aplicaciones como computadoras, routers, consolas de videojuego y algunos sistemas embebidos. Por esta razón, son las arquitecturas didácticas más utilizadas en ambientes universitarios. Estos procesadores han permitido enseñar los elementos básicos de una arquitectura de computadoras para un posterior aprendizaje de arquitecturas más complejas [30].

Académicamente existe una implementación llamada *MIPS-1 ISA*, está diseñada bajo una arquitectura simple que hace al estudiante buscar soluciones entre el desempeño y la disipación de energía, además de poder ser usado en actividades de varios cursos académicos: como *circuitos digitales, arquitectura de computadoras, sistemas operativos, compiladores y microprocesadores.*

Las principales características del microprocesador *MIPS-1* son: 32 registros de propósito general de 32-bit, arquitectura *RISC*, conjunto de 20 instrucciones, todas en formato de 32-bit, con 8 bits de operación de código, 4 bits para el registro de código, 4 bits para el registro destino y 16 bits para valores constantes. Son 20 las diferentes operaciones que puede realizar en el CPU y 11 códigos de operación reservados para instrucciones futuras [31].

Otra herramienta didáctica es la llamada *Cabare*, la cual utiliza una unidad de control basada en reconfiguración, puede ser usado en aplicaciones multimedia. *Cabare* es un procesador de propósito general diseñado con pocas instrucciones, está basado en el procesador didáctico *Altera*. Posee 11 registros de propósito general, un registro para el contador de programa (*PC*), una *ALU* con acumulador de registros y un registro *G* donde se mantienen los resultados de las operaciones realizadas por la ALU. Cuenta con 8 microinstrucciones de salto, y 8 operaciones que puede realizar la *ALU*. La memoria RAM tiene una longitud de datos de 32 bits [32].

Por su parte *MAC-1* es un procesador basado en una arquitectura microprogramada y usada para propósitos educativos. Está implementada en VHDL, se divide en 4 partes: *Control* (responsable de las operaciones), *Operativo* (operaciones de ellos), *RAM* (memoria que contiene el programa) y *Reloj*. Fue probada en una tarjeta NEXYS 2, con *Xilinx Spartan 3E FPGA XC3S500E* [33]–[35]. Su arquitectura microprogramada implementa el control del microprocesador a través de la memoria de programa [36].

El procesador **Sweet-16**, posee una arquitectura RISC de 16-bit su principal propósito es enseñar a los estudiantes con o sin conocimientos previos de electrónica digital o un HDL, es por esta razón que fue desarrollado para ilustrar y usarse en cursos de arquitectura de computadoras. La arquitectura del procesador Sweet-16, permite el uso del procesador para realizar ejercicios de programación, fue programado en lenguaje ensamblador, permitiendo que esté disponible en varios sistemas operativos [24].

En el *Centro Universitário Positivo* de *Curitiba, Brasil* en 2001, se llevaron a cabo prácticas donde se involucró un prototipo de un microprocesador de 4 bits con arquitectura *CISC* desarrollado con un HDL y probado mediante simuladores. En 2002 se agregaron pruebas en hardware, el FPGA fue configurado para realizar dichas pruebas. En 2003, se reemplazó la arquitectura CISC por RISC que ya incluyen pruebas de hardware, posteriormente en 2004 se incorporó un compilador para el procesador RISC [37].

El *mPd*, es un microprocesador de 8 bits, diseñado en VHDL, con arquitectura CISC; tiene características de conexionado con circuitos de memoria y sus dispositivos de entrada/salida son: *Bus de datos* de 8 bits, *Bus de direcciones* de 8 bits, *Mapa de memoria y mapa de entrada/salida independientes* de 256 direcciones cada uno, Línea M1: activa a nivel alto en los ciclos de búsqueda del código de operación, Dos líneas de petición de interrupción: INTO e INT1, activas a nivel alto y Una línea de petición de estados de espera, activa a nivel alto.

En cuanto al modelo de programación del mPd, cuenta con siete registros, todos ellos de 8 bits. El conjunto de instrucciones está formado por 19 grupos de instrucciones. La programación del mPd se realiza en lenguaje ensamblador mediante una hoja de Excel que permite elegir, mediante el nemotécnico, cada una de las instrucciones que forman el programa, así como el operando de la instrucción, en caso de que la instrucción elegida lo requiera [38].

El procesador **ANEM**, se desarrolló para ser usado como un microcontrolador. Una de sus principales características es el sistema de acceso a memoria basada en la arquitectura Harvard. Esta arquitectura consiste en usar la separación física de la memoria de datos y la memoria de programa, permitiendo accesos simultáneos entre ambas, dando como resultado un mejor funcionamiento, comparado con la arquitectura Von Neumann.

Para simplificar el diseño de la memoria del programa en *ANEM*, fue implementada usando bloques de memoria RAM disponibles en el propio *FPGA*. *ANEM* tiene canales alternos permitiendo a la memoria del programa sea cargada a través del puerto serial. Para que esto suceda, el programador debe estar habilitado (Prog pin debe mantenerse en nivel lógico alto), y el software debe enviar el código listo en formato binario siguiendo un algoritmo simple. El software fue desarrollado usando lenguaje de procesamiento para ejecutar las tareas del programa [39].

El procesador *ILA9200* está divido en varias unidades funcionales que han sido implementadas en un *ASIC*: *Unidad de control* que contiene un secuenciador de microinstrucciones, una *memoria de microprograma* de 256 palabras de 48 bits y *un registro de instrucción* de 16 bits; *unidad operativa* que contiene 14 registros de 16 bits distribuidos en dos bancos, *2 ALUs* cada una con sus registros de banderas y *registros dedicados* para el acceso a la memoria *RAM* de *programa* y *datos*; *unidad de comunicación* con el *Contador de Programa* (*PC*), contiene 6 *registros* mapeados en el espacio de memoria del PC mediante los cuales el usuario especifica las órdenes de monitorización del estado de los recursos en las otras 2 unidades [40].

El procesador *ILA9200* utiliza un microensamblador cuya función es traducir un conjunto de mnemónicos predefinidos en microinstrucciones de un microprograma.

Otra herramienta es **Neander** es una arquitectura didáctica y virtual conocida por su software emulador, el cual es usado para la enseñanza de arquitectura de computadoras y lenguaje ensamblador, es un procesador de 4-bit, cuya principal meta es evaluar el potencial de esta tecnología para propósitos educacionales y de investigación, la arquitectura fue adaptada a 4-bit, el conjunto de instrucciones está compuesto por 8 instrucciones [41].

La versión original de *Neander* es un simple procesador didáctico de 8-bit, todo el proyecto fue diseñado con la herramienta *CAD*. Ha sido usado por años en cursos de introducción a la arquitectura de computadoras en universidades brasileñas. Contiene 9 instrucciones, las cuales incluyen lógica y aritmética, bifurcación condicionante e incondicionante y la transferencia de datos en memoria.

Por su parte el procesador *SIC* está conformado de 5 registros internos (*A, X, L, PC y SW*) todos estos de 24-bit y con funciones específicas. Contiene 26 instrucciones de operaciones básicas con las características del procesador RISC, las instrucciones están divididas en: operaciones aritméticas, lógicas, comparación, desvío, carga, descarga y de entrada/salida [42].

Neander está compuesto por entidades simples que controlan el camino de datos y el flujo del programa, el direccionamiento de memoria es directo, entonces los datos siempre accederán a través de su posición en memoria. ALU considera dos entradas de 8-bit y 5 distintas operaciones. La interfaz de memoria está compuesta por tres buses (dirección, datos de entrada y salida y leer y escribir señales).

Tiene incluido tres modos de prueba, cada uno con un objetivo diferente, el primero es ayudar en las pruebas de registro simple para validar los flip-flop; el segundo modo prueba las funciones de ALU; y el tercero modo de prueba bloquea la prueba del temporizador, el cual controla toda la sincronización del circuito [43].

En la *Universidad Federal de Rio grande del Norte*, en *Natal, Brasil (UFRN)* se desarrolló un proyecto donde se utilizó el lenguaje VHDL para la descripción de la arquitectura y el procesador didáctico *MIC-1*, cuya parte operativa está constituida por una memoria de 16 registros de 16 bits, una ALU, dos registros con una memoria (*MAR* y *MBR*), shifter lógico (derecha/izquierda) y tres buses, dos de lectura y uno de escritura en memoria, para controlar las vías de datos son necesarias microinstrucciones de 32 bits. *MIC-1* es un microprocesador con un reloj basado en cuatro fases, que garantizan la correcta ejecución de sus instrucciones en un ciclo básico de la parte operativa.

El *MIC-1* no tiene instrucciones de entrada y salida, para esto utiliza, cuatro direcciones de memoria para acomodar un dispositivo de entrada (*0x0FFC* y *0x0FFD*) y un dispositivo de salida (*0x0FFE* y *0x0FFF*), las direcciones *0x0FFD* y *0x0FFF* son utilizados como registradores del estatus del dispositivo, mientras que las direcciones *0x0FFC* y *0x0FFE* almacenan un byte de entrada o salida, respectivamente [44].

En la *Universidad de Hiroshima* se utilizan las siguientes herramientas mediante las cuales los estudiantes pueden aprender los conceptos básicos de informática con la ayuda de un procesador de 16-bit llamado *TINYCPU*, un lenguaje ensamblador *TINYASM* y un compilador *TINYC*, a través de los cuales los estudiantes pueden entender fácilmente la arquitectura del procesador, programación en ensamblador y el diseño del compilador, respectivamente.

TINYCPU, TINYASM y TINYC fueron desarrollados utilizando Verilog HDL, Perl y Flex/Bison, respectivamente, para implementar y ejecutar TINYCPU se utilizó un FPGA en Spartan-3E y Spartan-3A.

El compilador TINYC traduce un programa basado en *C* en un lenguaje ensamblador para *TINYASM*. El lenguaje de programación *TINYC* soporta enteros de 16 bits con signo, instrucciones: *if*, *if-else*, *while*, *do while*, y la declaración *goto*. Además cuenta con operaciones aritméticas y lógicas básicas como suma, resta, multiplicación, negación, operaciones lógicas y de comparaciones.

Las herramientas *TINYCPU*, *TINYASM* y *TINYC* son utilizados para los cursos de hardware embebido y software embebido para estudiantes de posgrado [45].

Por otro lado en la *Universidad del Valle de Itajai* en *Brasil* (*UNIVALI*) se ha desarrollado los procesadores *BIP I* y *BIP II*, el cual utiliza una arquitectura basada en la arquitectura RISC del microcontrolador PIC de Microchip, utiliza el modelo Harvard, presenta un único registro para almacenamiento de datos, todas las operaciones se desarrollan en el acumulador, y todas las instrucciones están basadas en un único formato de instrucción y en dos modos de direccionamiento [46].

El procesador *BIP I* ésta basado en una arquitectura simple, con un conjunto de instrucciones (*ISA*) que incluye: carga, almacenamiento e instrucciones aritméticas; y al procesador *BIP II* se le agregan instrucciones condicionales e incondicionales. Ambos microprocesadores son empleados en algunos cursos en el área de ciencias de computación de *UNIVALI*, permitiendo que los estudiantes puedan mejorar su comprensión de los conceptos de arquitectura de computadoras.

Los atributos de las arquitectura de los procesadores *BIP I y BIP II*, incluyen: Arquitectura orientada al acumulador; ancho de datos de 16-bit; ancho de instrucciones de 16-bit; un solo tipo de dato (integer); un solo tipo de formato de instrucción; dos modos de direccionamiento (directo e indirecto); conjunto de instrucciones reducida (*RIS*); y, mapeo de memoria I/O. El procesador presenta muchas características de *RISC*, pero no puede ser considerado como tal, pues no cuenta con la arquitectura de carga-almacenamiento. El CPU tiene tres registros (*PC, ACC y STATUS*) [27].

*BIP I* cuenta con 8 instrucciones, mientras que el *BIP II* con 15. Utiliza arquitectura monocycle/Harvard, con dos memorias separadas.

Con el paso del tiempo el estudio y diseño de procesadores ha cambiado, así como las aplicaciones para el fin que han sido perfeccionados, han aparecido los procesadores de red los cuales fueron desarrollados usando modelos de arquitectura como *ASIP* (Application Specific Processor) y *SoC* (System-on-Chip), añadiendo la arquitectura *RISC* para un mejor desempeño computacional. Estos procesadores tienen un modelo de *ISA* específico para operaciones de red.

En la *Universidad Pontificia de Minas Gerais*, se desarrolló un simulador de un procesador didáctico de red, el cual fue construido con *C*++ y la principal interfaz es capaz de ayudar y guiar al estudiante en el aprendizaje del procesador de red y su funcionamiento [47].

De igual manera se ha desarrollado un procesador de red llamado *ASIP* que contiene instrucciones especiales para el acceso a nivel-bit a los registro de datos que se requieren al procesamiento de protocolo de comunicación orientado a paquetes. La arquitectura del procesador es *RISC* de 16 bits, con 12 registros de propósito general y extensiones especiales pata el acceso a los datos a nivel-bit. Se utilizó el compilador *LANCE* para la optimización de *ANSI C* [48].

#### 2.2 COMPILADORES Y HERRAMIENTAS DE DESARROLLO

Uno de los aspectos que han evolucionado de manera más visible son los *lenguajes de programación*. Los lenguajes de programación de *alto nivel* permiten al programador expresar algoritmos de manera concisa, pero ocasionan otro problema conocido como el llamado salto semántico, que es la diferencia entre las operaciones que proporcionan los lenguajes de alto nivel y las que proporciona la arquitectura de computadoras.

Para desarrollar programas de manera eficiente es necesario entender como son ejecutados estos en la computadora, y en ocasiones esto no se cumple, por ejemplo, es difícil entender la estructura de datos "puntero" si no se sabe cómo se implementa en lenguaje máquina.

Desafortunadamente muchos estudiantes inician su aprendizaje de un lenguaje de programación de alto nivel pero sólo a nivel de sintaxis y no se entiende la esencia de cómo se haría en inicio con un pseudolenguaje o en una lenguaje de bajo nivel, llevando a enfrentar un gran problema, la migración de la teoría a la práctica.

Para que un hardware sea funcional requiere de un software que ayude al usuario a interactuar con él. Se han propuesto una gran cantidad de herramientas: Se ha propuesto una herramienta que puede aceptar la sintaxis del lenguaje C y generar muchas versiones de los programas en ensamblador. Estos programas en ensamblador realizan las mismas funcionalidades definidas por el programa de entrada de C pero con diferentes comportamientos de *EMI* (electromagnet interference) conducidas cuando son ejecutados [49].

Es sabido que las herramientas de software de alto nivel (como C, C++, Python, JAVA, etc.) pueden ayudar a generar diferentes programas, como se pueden realizar en lenguaje ensamblador con la misma funcionalidad, pero con mayor número de instrucciones.

La arquitectura de un compilador puede ser dividido en cuatro partes: **Análisis léxico** (es el proceso en el cual se convierten la secuencia de caracteres en secuencia de tokens), **Gramática** (comprueba la gramática y construye una estructura de datos), **AST** (Abstract Syntax Tree, representa la relación de tokens) y **Generador de código** (convierte la optimización de los AST en salida como código ensamblador) [49].

Por otra parte *la optimización de código* representa varias consideraciones, como: *tiempo de ejecución efectivo* (optimización para instrucciones rápidas), *pocas instrucciones* (menor almacenamiento y menos memoria), *exportación de registros disponibles* (eficiente almacenamiento de registros) y *portabilidad*.

Otro diseño de un compilador fue desarrollado basándose en la herramienta **SUIF**. Este es un compilador de código abierto para los lenguajes *C* y *Fortran 77*. Este compilador se centra en identificar los patrones de comunicación en el tiempo de compilación, en otras palabras, se centra en la detección y análisis de los componentes de la comunicación del framework [33].

A lo largo de la historia se han diseñado herramientas que faciliten el desarrollo de un compilador, ya sea por completo o en cualquiera de sus fases como: **JastAdd** [35], es un sistema basado en java para construcción de compiladores, se centra en las representaciones del *árbol de sintaxis abstracta*. Su principal idea es definir cada aspecto del lenguaje en clases separadas para dar la posibilidad de usar todas las características del lenguaje de programación *JAVA*.

**AspectG** [50] fue creado para conseguir la interpretación modular con el lenguaje de definición **ANTL**; y **AspectASF** [51] tiene como objetivo especificar declarativamente qué reglas debe adaptarse para incorporar una semántica adicional.

Otra herramienta de apoyo para el desarrollo de compiladores es *LISA* el cual genera automáticamente un compilador y otras herramientas lingüísticas relacionadas con las especificaciones de lenguaje basados en atributos gramaticales formales. *LISA* consiste en definiciones regulares, definición de atributos, reglas (son las reglas de sintaxis generalizadas que encapsulan reglas semánticas), y métodos sobre dominios semánticos [52].

Por otra parte, ninguna de las herramientas disponibles en la actualidad apoya el desarrollo de los lenguajes incrementales. Por lo tanto, el diseñador del lenguaje tiene que diseñar nuevos lenguajes a partir de cero o por medio de la modificación de versiones anteriores. Así es como se desarrolló la herramienta *LISA* con la que los estudiantes tienen la posibilidad de experimentar, estimar y probar varios analizadores léxicos y sintácticos, *LISA* es un *IDE* en el cual los usuarios pueden especificar, generar, compilar y ejecutar programas de nuevos lenguajes especificados. El compilador/interprete generado por *LISA* es visualizado de manera similar como se muestra en [53].

LISA es una herramienta que facilita el aprendizaje y una comprensión conceptual de la construcción de compiladores. Se generó un analizador léxico o un escáner en Java para los autómatas finitos determinísticos (AFD); tokens del código del programa son agrupadas en frases gramáticas; cuando las sentencias son correctas, pueden ser computadas [54]-[55].

La mayor técnica de abstracción en ingeniería de software es dividir el sistema en componentes funcionales de tal manera que se pueda cambiar un componente en particular y no todo el sistema. Las propiedades correspondientes a las definiciones de lenguaje basados en gramáticas atributo son: definiciones regulares léxicas; definición de atributos; reglas generalizadas de sintaxis que encapsulan reglas semánticas; y, operación en dominios sistemáticos [56].

Combinar técnicas orientadas a objetos y conceptos necesarios con técnicas orientadas a aspectos permite logar una mejor modularidad, extensibilidad y reusabilidad. El *lenguaje* está dividido en dos partes principales: el *tipo de definiciones* y las *definiciones de variable*.

Otra herramienta que ayuda a la generación de compiladores es llamada **Coco/R** la cual toma atributos gramáticos y produce un escaneo analizador descendente, además analiza el contexto gramático (es decir, analiza la sintaxis), verifica atributos que pueden ser considerados como parámetros y acciones semánticas. Cada atributo gramático es procesado de izquierda a derecha. Mientras la sintaxis es analizada las acciones semánticas son ejecutadas [57].

Existen diferentes tipos de compiladores, los más comunes son los que pasan de un código de *alto nivel* (más entendible por el usuario, como código en lenguaje C o JAVA) a uno de *bajo nivel* (código maquina), pero también hay compiladores que pasan de *lenguaje ensamblador* a *código máquina*.

Como es sabido, diferentes combinaciones de código ensamblador pueden realizar la misma tarea, cada versión diferente de código es llamado Template; diferentes códigos pueden causar un comportamiento diferente de *EMI*, en otras palabras, es posible generar las mínimas de combinaciones de código ensamblador. Para realizar esto, primero se miden la ondas de cada una de las instrucciones; segundo, obtener la frecuencia de respuesta basándose en el estudio de la deducción del teorema *DFT*; y tercero elegir la frecuencia mínima de las combinaciones [58]-[59].

Las arquitecturas reales tienen un sinnúmero de referencias en el desarrollo y depuración de aplicaciones, aun así, el detalle de cada arquitectura es muy complejo; en cambio los simuladores proveen un mayor detalle de abstracción de la arquitectura.

Se ha desarrollado una plataforma que está formada por *hardware*, *firmware* y *herramientas de software*. El principal objetivo de este trabajo es el desarrollo de una plataforma donde se combine el software y hardware. Las herramientas de software para el desarrollo de esta plataforma son: *IDE*, *compilador* repositorio y *software* de programador [60].

#### 2.3 ENTORNO DE DESARROLLO INTEGRADO

El estudio de arquitectura de computadoras es fundamental en la formación de alumnos del área de computación, pues si se tiene una correcta asimilación de conceptos de arquitectura de computadoras, ayudan a fijar de mejor manera los conceptos de programación como por ejemplo: variables, declaración de variables, asignación de variables y su correspondencia con las operaciones de acceso a memoria (como asignación), además de vectores, punteros, niveles de lenguaje, operaciones aritméticas entre otros más.

La elección de un procesador para enseñar correctamente la lógica de programación y conceptos de arquitectura de computadoras, debe facilitar el establecimiento de relaciones entre las abstracciones lógicas necesarias para programación y la implementación de estas abstracciones en hardware. La elección del procesador también debe de priorizar aspectos didácticos que favorezcan la comprensión de las relaciones entre software y hardware en un enfoque multidisciplinario.

El objetivo de desarrollar una arquitectura de referencia para la enseñanza de conceptos en el área de arquitectura y organización de computadoras es proveer una base necesaria para la comprensión de abstracciones presentadas en los cursos de algoritmos, programación, sistemas digitales, sistemas operativos.

Existen diferentes disciplinas donde se abarca a detalle el estudio de arquitecturas y sistemas de software relacionadas con esto, existen dos ideas que pueden ser utilizadas: el uso de arquitectura de procesadores reales o de simulaciones.

Como se ha mencionado, los cursos de arquitectura de computadoras juegan un papel importante en el desarrollo de habilidades y destreza en ciencias de computación y en cursos de ingeniería, especialmente para los que trabajan con el diseño de sistemas embebidos.

Los procesadores se deben basar en arquitecturas alternativas más simples con el fin de facilitar la programación y la construcción de un procesador: arquitectura basada en acumulador; todas las instrucciones deben estar basadas en un forma de instrucciones simples; dos modos de direccionamiento (inmediata y directa).

Al uso de procesadores con fines didácticos, se le debe de dar un enfoque *multidisciplinario*, es decir, deberían de ser utilizados en varias asignaturas antes mencionadas, para así, poder ayudar a los alumnos a asimilar mejor los conceptos de cada una de las asignaturas, relacionando conceptos entre sí.

El conocimiento de la operación de las computadoras es muy importante, ya que permiten a los estudiantes entender conceptos del área de programación, de esta manera, los profesores de las materias de introducción a la programación utilizan abstracciones de conceptos de arquitectura de computadoras para representar algunos de sus conceptos para permitir a los alumnos un mejor entendimiento de esta materia.

En la *Universidad de Pisa* desarrollaron un ambiente llamado *Csim2*, el cual permite al estudiante familiarice con conceptos de localidad de programa, estructura del cache y ajuste de rendimiento, mientras la producción actual del dato se analiza por el software que se encuentra con el sistema embebido, de esta manera los estudiantes pueden analizar el comportamiento del programa [61].

El ambiente educacional del *Csim2* ayuda a combinar dos exigencias complementarias de los cursos de arquitectura de computadoras de los sistemas embebidos: *Disponibilidad de una herramienta* (la cual provee ejemplos prácticos para mostrar los principales conceptos de la arquitectura de sistemas embebidos) y por otro lado, *fomentar* en los estudiantes a la *actividad de diseño real de sistemas* orientados a aplicaciones integradas.

En *UNIVALI* [46] se ha desarrollado e implementado un *IDE* (BIPIDE) con la finalidad de crear un ambiente amigable para el usuario al momento de estudiar el funcionamiento de los procesadores arquitecturas *RISC* de 16-bit creado con propósitos educativos, en la que se integran dos herramientas: un *compilador* en lenguaje *Portugol* y un *simulador* de un procesador (ya sea el BIP I o BIP II).

**BIPIDE**, ofrece un enfoque interdisciplinario que reduce el grado de abstracción de conceptos como: uso de memoria, operaciones aritméticas, desvíos y lazos. Presenta tres módulos principales:

- Programación: permite que el usuario escriba y compile sus propios programas;

- Simulación: permite simular los programas desarrollados; y

- Ayuda: presenta información respecto a la funcionalidad del sistema y sobre la arquitectura y organización de los procesadores BIP [62].

# **CAPÍTULO 3. MARCO TEÓRICO**

En este capítulo se desarrollarán conceptos teóricos necesarios para poder comprender la implementación del IDE, mostrando la arquitectura, características, modo de direccionamiento y conjunto de instrucciones del procesador SOPHIA. Posteriormente describiremos los tipos de compiladores y sus diferentes fases. Por último se describirán los simuladores y sus características.

#### 3.1 PROCESADOR DIDÁCTICO SOPHIA

El procesador didáctico SOPHIA nace por la necesidad de tener una herramienta que ayude en el proceso de aprendizaje en los cursos de arquitectura de computadoras, está implementado en un *FPGA* para ser una librería.

# **3.1.1 CARÁCTERISTICAS Y ARQUITECTURA**

- Basado bajo la arquitectura Harvard.

- Conjunto de instrucciones RISC

- Instrucción simple Dato simple (SISD)

- Memoria ROM de 256 localidades de 16-bits.

- Memoria RAM de 256 localidades de 8-bits.

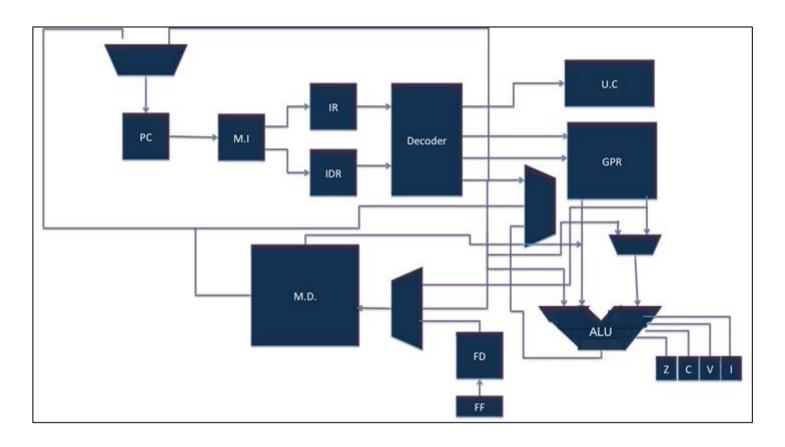

La arquitectura del procesador que se muestra en la Figura 3.1, se puede observar la unidad de control, la memoria de instrucciones, de datos, el decodificador de instrucciones, unidad de control, registros de propósito general, la unidad aritmético-lógica, las banderas y el apuntador de pila.

Figura 3. 1 Arquitectura del procesador SOPHIA.

PC – Contador de programa. M.I – Memoria de Instrucciones. ALU – Unidad Aritmético-Lógica

Decoder – Decodificador. U.C – Unidad de Control. GPR – Registros de Proposito General. M.D. – Memoria de Datos.

Z – Bandera Cero. C – Bandera Acarreo. V – Bandera Sobreflujo. I – Bandera Interrpución. FF – Última localidad

#### **3.1.2 CONJUNTO DE INSTRUCCIONES**

En la Tabla 3.1 se muesta el conjunto de instrucciones que contiene 29 instrucciones de una longitud de 16 bits, las cuales se dividen en cinco grupos (saltos, un registro con datos inmediatos, dos registros, un registro y directas, es decir sólo el nemónico).

#### 3.1.3 MODOS DE DIRECCIONAMIENTO

Se tienen diferentes tipos de direccionamiento, dependiendo de la naturaleza de las instrucciones, la distribución de los 16 bits que componen cada instrucción se puede observar en la Tabla 3.1. Los modos de direccionamiento se muestran a continuación:

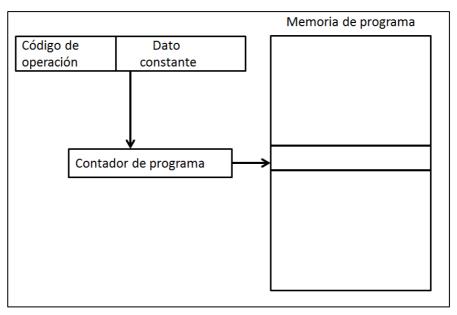

#### Directo a memoria.

Cuando una dirección en la memoria de programa es direccionada por el contador de programa propicia que el valor de 8 bits se cargue. Este direccionamiento corresponde a la categoría de saltos. Figura 3.2.

Figura 3. 2 Direccionamiento directo a memoria, donde el código de operación define el tipo de slto y dato constante el nímero de la próxima instrucción a ejecutar.

Tabla 3. 1 Conjunto de instrucciones del procesador SOPHIA

|      |               |                                  |                |                                         | Formato de instrucción de 16 bits |    |     |    |    |    |    |    |     |     |     |     |   |   |   |   |        |

|------|---------------|----------------------------------|----------------|-----------------------------------------|-----------------------------------|----|-----|----|----|----|----|----|-----|-----|-----|-----|---|---|---|---|--------|

|      |               |                                  |                |                                         |                                   | Ol | COE | DE |    |    |    |    | PAF | RÁM | ETF | ROS |   |   |   |   |        |

| No.  | Nemónico      | Descripción                      | Sintaxis       | Micro-<br>operación                     | 15                                | 14 | 13  | 12 | 11 | 10 | 9  | 8  | 7   | 6   | 5   | 4   | 3 | 2 | 1 | 0 | Ciclos |

| Tipo | saltos        |                                  |                |                                         |                                   |    |     |    |    |    |    |    |     |     |     |     |   |   |   |   |        |

| 1    | JMP           | Salto directo                    | JMP k          | PC ← k                                  | 0                                 | 0  | 0   | 0  | 0  | -  | -  | -  | k   | k   | k   | k   | k | k | k | k |        |

| 2    | BRC           | Salto bandera acarreo            | BRC k          | Si (C=1)<br>PC ← k<br>Sino<br>PC ← PC+1 | 0                                 | 0  | 0   | 0  | 1  | 1  | 1  | -  | k   | k   | k   | k   | k | k | k | k |        |

| 3    | BRZ           | Salto bandera cero               | BRZ k          | Si (Z=1)<br>PC ← k<br>Sino<br>PC ← PC+1 | 0                                 | 0  | 0   | 1  | 0  | -  | -  | 1  | k   | k   | k   | k   | k | k | k | k |        |

| 4    | BRV           | Salto bandera sobreflujo         | BRV k          | Si (V=1)<br>PC ← k<br>Sino<br>PC ← PC+1 | 0                                 | 0  | 0   | 1  | 1  | -  | -  | -  | k   | k   | k   | k   | k | k | k | k |        |

| 5    | JRS           | Salto regreso a subrutina        | JSR k          | [SP] ← PC<br>SP ← SP-1<br>PC ← k        | 0                                 | 0  | 1   | 0  | 0  | -  | -  | -  | k   | k   | k   | k   | k | k | k | k |        |

| Tipo | un registro c | on un dato inmediato             |                |                                         |                                   |    |     |    |    |    |    |    |     |     |     |     |   |   |   |   |        |

| 6    | ADDI          | Suma inmediata                   | ADDI Rd, k     | $Rd \leftarrow Rd + k$                  | 0                                 | 1  | 0   | 0  | 0  | Rd | Rd | Rd | k   | k   | k   | k   | k | k | k | k |        |

| 7    | SUBI          | Resta inmediata                  | SUBI Rd, k     | Rd ← Rd - k                             | 0                                 | 1  | 0   | 0  | 1  | Rd | Rd | Rd | k   | k   | k   | k   | k | k | k | k |        |

| 8    | ANDI          | Y inmediato                      | ANDI Rd, k     | $Rd \leftarrow Rd AND$<br>k             | 0                                 | 1  | 0   | 1  | 0  | Rd | Rd | Rd | k   | k   | k   | k   | k | k | k | k |        |

| 9    | ORI           | O inmediato                      | ORI Rd, k      | $Rd \leftarrow Rd OR k$                 | 0                                 | 1  | 0   | 1  | 1  | Rd | Rd | Rd | k   | k   | k   | k   | k | k | k | k |        |