## Institutionen för systemteknik

Department of Electrical Engineering

Examensarbete

Master's Thesis

## Implementation Aspects of Image Processing

Per Nordlöw

LITH-ISY-EX-3088

Mars 2001

#### Abstract

This Master's Thesis discusses the different trade-offs a programmer needs to consider when constructing image processing systems. First, an overview of the different alternatives available is given followed by a focus on systems based on general hardware. General, in this case, means mass-market with a low price-performance-ratio. The software environment is focused on UNIX, sometimes restricted to Linux, together with C, C++ and ANSI-standardized APIs.

# Contents

| Ove | erview                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Par | allel Processing                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1 | Sequential, Parallel, Concurrent Execution                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.2 | Task and Data Parallelism                                                                                           | <b>6</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3 | Architecture Independent APIs                                                                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 2.3.1 Parallel languages                                                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 2.3.2 Threads $\ldots$                                                                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 2.3.3 Message Sending Interfaces                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Cor | nputer Architectures 1                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1 | Flynn's Taxonomy                                                                                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.2 |                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.3 | Data Locality                                                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.4 |                                                                                                                     | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.5 |                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6 | •                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.7 |                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.8 | SWAR                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 3.8.1 SWARC and Scc                                                                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | <u> </u>                                                                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.9 | Reconfigurable Computing                                                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.9.2 Mixed Architectures                                                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Imr | plementation Aspects 2                                                                                              | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -   | -                                                                                                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2 |                                                                                                                     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 0 1                                                                                                                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 1                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                                                                                                                     | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 1                                                                                                                   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.3 |                                                                                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | Par<br>2.1<br>2.2<br>2.3<br>Cor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>Imp<br>4.1<br>4.2 | 2.1Sequential, Parallel, Concurrent Execution2.2Task and Data Parallelism2.3Architecture Independent APIs2.3.1Parallel languages2.3.2Threads2.3.3Message Sending Interfaces2.3.3Message Sending Interfaces <b>Computer Architectures</b> 13.1Flynn's Taxonomy3.2Memory Hierarchies3.3Data Locality3.4Instruction Locality3.5Shared and Distributed Memory3.6Pipelining3.7Clustered Computing3.8.1SWAR3.8.1SWARC and Scc3.8.2SWAR in gcc3.9.1Reconfigurable Computing3.9.2Mixed Architectures24.1.1Martix Storage Techniques4.2.2Element Components4.2.3Matrix Storage in C4.2.4Regions Of Interest in C4.2.5Access Techniques in C4.2.6C++ Implementation |

### CONTENTS

|        | 4.4                      | Perform                                       | nance Tricks Summary       | 33                          |

|--------|--------------------------|-----------------------------------------------|----------------------------|-----------------------------|

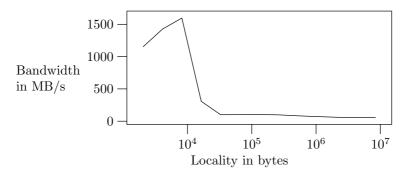

|        | 4.5                      | Measur                                        | ring Data Locality         | 34                          |

|        |                          | 4.5.1                                         | Measuring Memory Bandwidth | 34                          |

|        | 4.6                      | Using I                                       | Locality                   | 36                          |

|        | 4.7                      | The So                                        | bel Operator               | 36                          |

|        | 4.8                      | Graph                                         | Representation             | 37                          |

|        | 4.9                      | Graph                                         | Implementation             | 37                          |

|        |                          | 4.9.1                                         | Graph Objects              | 38                          |

|        |                          | 4.9.2                                         | Node Methods               | 38                          |

|        |                          | 4.9.3                                         | Graph Methods              | 39                          |

|        |                          | 4.9.4                                         | Testing Concepts           | 42                          |

|        |                          |                                               |                            |                             |

| F      | ۸d                       |                                               | log input                  | 45                          |

| 5      | Ado                      | ling vid                                      | leo input                  | 45                          |

| 5<br>6 |                          | 0                                             | -                          | 45<br>48                    |

| -      |                          | tem Re                                        | strictions                 | 48                          |

| -      | Sys                      | t <b>em Re</b><br>Power                       | strictions<br>Consumption  | <b>48</b><br>48             |

| -      | <b>Sys</b><br>6.1        | t <b>em Re</b><br>Power<br>Respon             | strictions<br>Consumption  | <b>48</b><br>48<br>48       |

| -      | <b>Sys</b><br>6.1        | tem Re<br>Power (<br>Respon<br>6.2.1          | strictions<br>Consumption  | <b>48</b><br>48<br>48<br>49 |

| -      | <b>Sys</b><br>6.1        | tem Re<br>Power (<br>Respon<br>6.2.1          | estrictions<br>Consumption | <b>48</b><br>48<br>48<br>49 |

| -      | <b>Sys</b><br>6.1<br>6.2 | tem Re<br>Power (<br>Respon<br>6.2.1<br>6.2.2 | estrictions<br>Consumption | <b>48</b><br>48<br>48<br>49 |

## Chapter 1

# Overview

As long as Moore's Law continues to double the transistor density in computers approximately every 18 months, more advanced operations can be performed on larger data sets in shorter amounts of time. In the field of image processing this means that more complex features of digital images can be extracted within time limits small enough to be used in situations where the computing devices have limitations in size, weight and power consumption.

But these speedups are often theoretical and in practise they do not come automatically. This means that developers, who want to make efficient use of new computer systems, first have to spend a lot of time learning new development tools and understanding these systems' possibilities and limitations.

Because the image processing algorithms used are normally already known and implemented in some high-level language, the implementation instead becomes a *code conversion*. As this often is a very time consuming and, for most users, uninteresting process, it is important to develop tools that can *automate* as many steps in this process as possible.

The purpose of this Thesis can followingly be divided into these main parts:

- Overview the hardware and software choices we have when implementing image processing operations on systems with high performance demands and restrictions mainly in power consumption and response time.

- When automatic code conversion is possible briefly discuss it and look at the tools available.

- In more detail investigate the possibilities of using general desktop PC hardware together with open software to design a real-time video processing system.

The following description overviews the chapters of this Thesis:

Chapter 2 briefly describes the different paradigms of parallel computing.

Chapter 3 overviews different types of computer architectures.

**Chapter 4** then applies these concepts which results in a guideline on how to construct an image processing systems that automatically takes advantage of locality and scalability. At the end of the chapter, the key steps of this

guideline are then experimentally exemplified. The Sobel operation follows through the guideline and gives the reader examples of how theoretical concepts are applied.

- **Chapter 5** explains how I add a video source to the system, described in Chapter 4, by plugging in a non-expensive PCI TV-card. Here I also try to answer the question of how complicated image processing there is time for on the video stream grabbed from the TV-card.

- **Chapter 6** discusses additional system restrictions associated with power consumption and choice of Operating System (OS).

- Chapter 7 finally summarizes all the previous chapters and draws related conclusions.

| Abbreviation | CPU                                   | RAM     |

|--------------|---------------------------------------|---------|

| TS $1$       | AMD K6-2 300MHz                       | 192  MB |

| TS $2$       | $2 \times$ Intel Pentium Xeon 300 MHz | 2  GB   |

| TS $3$       | Sun UltraSPARC-IIi 440-MHz            | 256  MB |

| TS 4         | $4$ $\times$ Sun UltraSPARC-II 400MHz | 4  GB   |

Performance of the algorithms are measured on the following test systems (TS):

# Chapter 2

# Parallel Processing

Parallel Processing refers to the concept of reducing the execution time of a calculation by dividing the problem into multiple parts. By making these parts execute indepently and simultaneously, we can draw advantage of the different multiprocessor architectures that are becoming more and more popular today.

Before designing or using such a system there are some things we have to take into consideration and the following sections will try to categorize and describe these. It is important to understand that, in practise, the hardware and the software developer must work together to optimally utilize the ideas of parallel processing.

## 2.1 Sequential, Parallel, Concurrent Execution

Most programs are today designed to execute in a sequential order, i.e. a previous part of the program has to complete its execution before the subsequent part can begin its execution. This approach works fine on uni processors (UP) systems (systems with one processor) but when it comes to making good use of multi processor (MP) systems (systems with more than one processor) the execution models become more complicated, and some parts of the program has to be rewritten to enable parallelism in execution.

As good as every modern computer is using an operation system (OS) that supports *multitasking*. These are examples of systems in which the programs in the system execute *concurrently*. In this case this means that multiple processes or multiple parts of a program (threads) share the processing in the computer over time eventhough there may be only one processor installed at the time. This is also called "timeslice-sharing" of processing. The sharing and scheduling of these are, as said above, hidden in the OS and to the application programmer the tasks "appear" to execute in parallel.

## 2.2 Task and Data Parallelism

There are basically two main approaches we can use when adding parallelism to an algorithm.

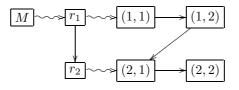

The first one, referred to as *task parallelism* or *functional decomposition* tries to exploit independencies between different parts of the program in order

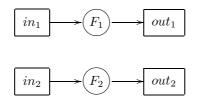

to reschedule these to execute in parallel. As an example, Figure 2.1 illustrates two different functions  $F_1$  and  $F_2$  that operate in parallel on their arguments  $in_1$ ,  $out_1$ ,  $in_2$  and  $out_2$ .

Figure 2.1: Task Parallelism

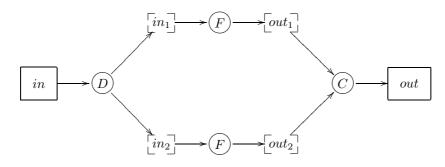

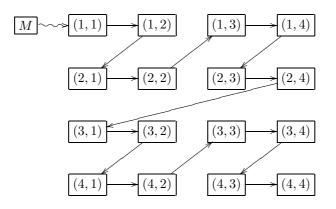

The second one, referred to as *data parallelism* or *domain decomposition* searches for a way to divide the data being processed into parts that can be operated on independently of each other. As an example, Figure 2.2 illustrates two instances of the same function F being applied in parallel on two separate parts of the data sets *in* and *out*. D and C represent the domain decomposition and composition stages respectively.

Figure 2.2: Data Parallelism

## 2.3 Architecture Independent APIs

When it comes to the real implementation stage of parallel algorithms there are several different tools or APIs to use, each suitable for different classes of problems. In this section we will summarize some Application Programming Interfaces, or APIs, that can be regarded as general and independent of the computer architecture on which the compiled code is supposed to execute.

#### 2.3.1 Parallel languages

The first and perhaps the most simple way to make use of MP-systems is to use a programming language in which you can specify parallelism. Examples of these are Compositional C++ (CC++), pC++, Fortran M (FM) and High Performance Fortran (HPF). These languages give the programmer a high level interface with which he can express his parallel thoughts. The disadvantage is limited platform support because they are bound to a special set of hardware architectures.

- $\mathbf{CC}$ ++ <sup>1</sup> is a small set of extensions to C++ which as of today are targeted for task parallelism. These extensions give the programmer control over locality, concurrency, communication and mapping. In the future focus will be on the High Performance C++ (HPC++) which is a joint project between the CC++ group and the data parallel pC++ project. The goal is to offer both data- and task parallelism.

- **FM**  $^2$  is a small set of extensions, that add support for tasks and channels in Fortran (Formula translation). A special feature of FM is that it can guarantee programs to be *deterministic*, which means that two executions with the same input will give the same output.

- **HPF** <sup>3</sup> extends Fortran 90 to provide access to high-performance architecture features while maintaining portability across platforms.

#### 2.3.2 Threads

A more general and portable but also lower-level way of expressing both task and data parallelism in a computer program is to use *threads*. On UP-systems its main purpose is to enable concurrent execution of different parts of a process. On some MP-systems (systems with more than one processor) these threads are automatically distributed over all processors. Threading is also useful in client-server communication and in GUIs where several tasks need to respond to requests simultaneously.

One can think of threads as "mini-processes" inside a process that, in contrast to the process which has sole possession of its resources, all share the *same resources*, such as file descriptors and allocated memory. In practise, threads are used by calling a set of threading-functions from a library. These functions control the construction, communication, synchronization, and destruction of the threads.

There exists several different threading APIs — all with their own interfaces. When portability is of great concert, the standardized and widely used "POSIX Threads API" (P1003.1c) should be used.

#### 2.3.3 Message Sending Interfaces

When it comes to making use of clustered computers, i.e. computers connected to each other through a high-speed network, another technique is used to explore parallelism. Because of the high communication latencies and the relatively low bandwidth of the systems one often wants to minimize the data sent between each process. Therefore the programmer explicitly specifies the messages that are sent between the different processing elements. The most commonly used APIs for this purpose are MPI (Message Passing Interface) and PVM (Parallel Virtual Machine).

<sup>&</sup>lt;sup>1</sup>http://www.compbio.caltech.edu/ccpp/

<sup>&</sup>lt;sup>2</sup>http://www.netlib.org/fortran-m/index.html

<sup>&</sup>lt;sup>3</sup>http://www.crpc.rice.edu/HPFF/home.html

If the programmer needs to go down to a lower level of the network communication it is common to make use of a Socket API, e.g. BSD Sockets on an UNIX environment, and Winsock on a Windows based machine. Here, the programmer can specify exactly how the network communication should take place and thus avoid all unnecessery overhead that might occur if we only need a small set of functionality in our communication.

See Table 2.1 for a summary of the APIs mentioned above. The Center for Research on Parallel Computation  $(CRPC)^4$ , could also be of interest.

|               | Parallelism |      |  |

|---------------|-------------|------|--|

| API           | Task        | Data |  |

| CC++          | Yes         | No   |  |

| pC++          | No          | Yes  |  |

| HPC++         | Yes         | Yes  |  |

| $\mathbf{FM}$ | Yes         | Yes  |  |

| HPF           | Yes         | Yes  |  |

| Threads       | Yes         | Yes  |  |

| MPI, PVM      | Yes         | Yes  |  |

Table 2.1: Parallel Processing APIs.

<sup>&</sup>lt;sup>4</sup>http://www.crpc.rice.edu/CRPC/

## Chapter 3

# **Computer Architectures**

## 3.1 Flynn's Taxonomy

The usual method for categorizing different kinds of computer architectures on a higher and more theoretical level is to use Flynn's Taxonomy. It describes the parallelism in terms of a *data* stream and an *instruction* stream as follows.

- **SISD** or Single Instruction Single Data (SISD), represents the conventional way of looking at a computer as a serial processor—one single stream of instructions processes one single stream of data.

- **SIMD** or Single Instruction Multiple Data (SIMD), is the most commonly explored parallelism in the microprocessors for todays desktop PCs. This approach reduces both hardware and software complexity compared to MIMD but is suitable only for special kinds of problems which contain much regularity, such as, *image processing, multimedia, signal processing* and certain numerical calculations.

As the first two of these are popular in today's mass-market consumer applications, it is therefore profitable to use SIMD-techniques in processors of these systems. The well-known extension MMX, 3DNow! and AltiVec are all examples of the special SIMD technique SWAR, which will be further discussed in Section 3.8.

For industrial applications digital signal processors, or DSPs, are popular architectures for analyzing digitized analog signals. These are also based on the SIMD idea.

- **MISD** or Multiple Instruction Single Data (MISD), does not really occur as a real-world example of an architecture but is rather here in order to complete the taxonomy. The idea of executing a series of instructions on the same set of data is not totally alien though. One could say that instruction pipelining, belongs to this category. This however occurs at the sub-assembly level in the processor and is not something that the programmer has to care about, not even the assembly programmer.

- **MIMD** or Multiple Instruction Multiple Data (MIMD), is the most general architecture of the above mentioned. In this we have the ability to explore

both task and data parallelism at the same time. In most OSs the task parallelism is automatically used when executing different processes all with their own private resources. But there is also the possibility of using task parallelism inside of a process, using threads which we discussed in Section 2.3. Examples of MIMD-machines are the MP-systems often used in large LAN and web servers. Sometimes we impose a restriction on the MIMD idea by making all processors run the same program, and we say that such a system belongs to category of Single Program Multiple Data (SPMD) systems. Opposite to SIMD, each processor can in this case take a different execution path through the program. Programs parallelized through MPI or PVM execute in this way.

Architectures of today do not necessary fit distinctively into one of these categories but instead more often makes use of some or all of them. Therefore the purpose of the taxonomy is rather to provide developers with a set of theoretical concepts with which they can express their thoughts and ideas.

## **3.2** Memory Hierarchies

Probably the most important and fundamental architectural principle around which computer systems have been built and are being built is often called the "90–10 Rule". This rule states that on average

#### 90~% of the operations are performed in 10~% of the code.

To take advantage of this assumption, we should try to organize the memory as a *hierarchy*. On the highest level we have the smallest sized but also the fastest memory and vice versa. At all levels except the lowest the data being kept in the memory is actually only a mirror of the memory kept in the lowest. When a program is repeatedly using a small part of the data at some level, it first copies it to the highest suitable memory level before the processing of it starts. Of course when the processor changes data that is not placed in lowest level the original copy has to be updated. Therefore

#### A write operation is on average more time-consuming than a read operation.

A typical modern PC usually has a memory hierarchy that consists of at least five levels. At the first level usually lies the interal registers accessible without any delay at all. Then comes the L1 Cache, which is usually placed right besides the logic gates on the microprocessor. Often the first half of it is used for instructions and the second half for their data. The third level, normally referred to as the L2 Cache, normally sits on top of the microprocessor and has an access latency of a couple of clock cycles. In some CPUs, such as the Alpha processors, a L3 Cache is also present. See Table 3.1 for details.

Next we have the primary memory. Here, accesses are limited by the external bus speed. Today the most dominating bus type on PCs is the 32-bit PCI bus (Peripheral Component Interface) running at 33 MHz, thus providing a peak-bandwith of  $4 \cdot 33 = 132$  Megabytes per second. The PCI bus is optimized for burst-reads of data and its peak bandwidth is only achieved in applications where a large degree of data parallelism, as in image processing, is present. In

| Memory Type       | Access Latency |

|-------------------|----------------|

| Register          | 2ns            |

| L1 on-chip cache  | 4ns            |

| L2 on-chip cache  | 15ns           |

| L3 off-chip cache | 30 ns          |

| Main Memory       | 220ns          |

Table 3.1: Memory hierarchy in a 500MHz DEC 21164 Alpha.

cases of individual reads and writes of 32-bit integers that bandwidth is normally decreased to around a fourth of its peak bandwidth.

The next level normally called secondary memory and is often a harddisk.

The last level would in most consumer applications not be regarded as a memory but rather a communication level. But in the cases of networked workstations connected to a centralized file server or clustered computers with local harddisks it indeed belongs to the memory hiearchy and is used as a such.

## 3.3 Data Locality

Memory hierarchies are present in all modern computer systems and the number of levels and their relative differencies in bandwidth and access latency are constantly increasing. As an example, the external bandwidth of the PCI-bus has not changed at all during the last six years compared to the L1 cache today operating at the internal CPU frequency which double approximately every 18 months.

Adapting our code so that it makes use of this property is therefore a *long-term* and *platform indepedent* way of optimizing our algorithm. Such an implementation is said to use *locality*.

Traditionally, the definition of locality can be formulated like

For each memory reference, perform as many operations as possible.

This rule is, however, out of date, as it assumes only two memory levels—the primary memory and the CPU registers. A more up to date definition would instead be formulated like

For each new reference of an element at a specific memory level, reuse the element in operations at higher memory levels as much as possible.

## **3.4** Instruction Locality

The same rules of locality also apply to the organization and execution of the program code.

- When the code is compiled into CPU instructions, reuse of functions gives good locality.

- The same goes for interpreted code, but here the interpreter can be provided with extra functionality that enables run-time restructuring of the

code according to historical information about which parts of the code that is most commonly used. A good example of this, is the constant advances being made in the Java interpreters.

As good as all OSes provide shared libraries, that contain common functions used by many application. If performance has the highest priority, it can be a good idea to include these functions in the executable, which instead prioritizes instruction locality and performance before memory usage.

## 3.5 Shared and Distributed Memory

There are basically two main branches of MIMD memory architectures; Shared Memory Architectures and Distributed Memory Architectures.

Traditionally the difference lay in the organization of the memory. If all processors shared a common memory we had a shared memory architecture with a high interconnection bandwidth. If we, on the other hand, preferred high local bandwidth we instead chose a distributed memory architecture.

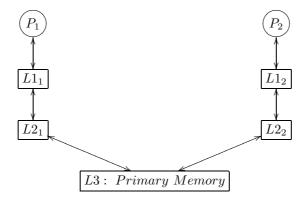

As the number of stages in memory hierarchies are constantly increasing, the separation into shared and distributed memory systems is no longer distinct. For example, all MP-systems for the Pentium Processor and later have a shared primary memory together with separate L1 and sometimes L2 caches. See Figure 3.1 for an illustration.

Figure 3.1: Memory hierarchy in an MP-system with two processors  $P_1$  and  $P_2$ , each having separate L1 and L2 caches together with a shared primary memory.

This design is another result of the "90–10 Rule" defined in Section 3.2. Because the bottleneck in such MP-systems is the bandwidth of the primary memory, locality in this case becomes crucial to performance. Briefly stated this means that

The scalability in shared memory MP-systems increases with the locality.

## 3.6 Pipelining

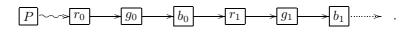

*Pipelining* is the concept of dividing a complex operation into several consecutive less complex operations that operates on a stream of data which contains a high

degree of data parallelism. Just as the maximum throughput of oil in a pipeline is directly related to its thinnest part, the maximum throughput of such a computational pipeline is linearly dependent on the throughput of the slowest stage in the pipeline.

Therefore, if we want to make efficient use of the hardware on which we are to implement our algorithm, it is important to carefully examine which stages in the pipeline that take the longest time to finish. Once we have this knowledge we can focus our optimization efforts on these stages.

Pipelining is extensively used in the construction of arithmetic units of microprocessors but we can also, in conjuction with ideas of memory hierarchies and cache memories, make use of it in the design of software, especially image processing software. See Figure 3.2.

$$in \longrightarrow S_1 \longrightarrow S_2 \longrightarrow S_3 \longrightarrow out$$

Figure 3.2: Computational pipeline with 3 stages  $S_1$ ,  $S_2$  and  $S_3$ .

## 3.7 Clustered Computing

Clustered Computing is a new trend in the construction of large parallel computer systems. It uses ordinary home PCs together with a high speed network to construct a parallel machine. For special kinds of applications its largest advantage, in comparison with other architectures such as SMP systems, is its very low *price-performance ratio*. This is because it uses standard PC workstations as its building blocks, often called Mass-Market Commercial Off The Shelf (M<sup>2</sup>COTS) hardware.

Its largest disadvantange is its inter-communication bottleneck. Therefore clustered computers are only competitive when doing computations that are not dependent on low communication latencies and high bandwidths. Typical areas that fit these restrictions are physical simulations and ray tracing.

It is very popular to use Linux as the OS on a clustered system since it is free, has excellent networking hardware and protocol support, and has an open source. The Beowulf Project is an example of this and it uses only Linux when developing its cluster software platform BPROC.

Other popular APIs in the area are the traditional PVM and the newer MPI upon which much cluster software has been built. If one is interested in more optimized network communication, that is controlling individual network packets, one has to go down one level to the socket layer, described in Section 2.3.

Another important factor is how the individual processing nodes are connected to each other, the network *topology* of the cluster. BPROC has tried out different topologies with the experience that the *linear switched* network, with its general high performance, is to prefer. Otherwise, the programmers tend to make the software too specialized.

From an image processing point of view these technologies could come in handy in the future as the access latencies decreases and bandwidths keep on growing. In fact, disregarding the access latencies and the non-deterministic transmission time of Ethernet, the peak bandwidth of Gigabit Ethernet is actually sufficient to make clusters useful in image processing.

## **3.8 SWAR**

SWAR<sup>1</sup>, which stands for "SIMD Within A Register", is a general name for the concept of treating an *m*-bit (*m* is normally 64 or 128) processor register as a set of *n* (typically 2, 4, 8, ...) smaller m/n-sized registers. Operations are then performed in parallel on these *m*-bit wide sub-fields.

Some SWAR operations can be performed trivially using ordinary m-bit integer operations, without concern for the fact that the operation is really intended to operate independently in parallel on n sub-fields. Such a SWAR operation is said to be *polymorphic*, since the function is unaffected by the field types (sizes). Testing if any field is non-zero is polymorphic, as are all bitwise logic operations. Most other operations are not polymorphic though, and special hardware is often constructed when high performance of operations with sub-field precision is wanted.

Many high-end microprocessors have, within the recent 5 years, added specialized machine instructions that increase the performance of SIMD-operations. The most well-known example of this is the MultiMedia eXtension set (MMX) which first appered in the Intel Pentium MMX processor. This instruction set is now a standard component in all of Intel's 32-bit architectures (IA-32) compatible with the Pentium processor. Other vendors, specifically Cyrix and AMD, have also chosen to implement MMX in their microprocessors, thus providing total compatibility with the Pentium MMX processor, an important issue in the consumer mass-market for Windows compatible CPUs.

#### 3.8.1 SWARC and Scc

Table 3.2 lists other architectures with SWAR extensions in their instruction sets. Aside from the three vendors Intel, AMD and Cyrix who have agreed on MMX, all of these instruction set extensions are roughly comparable, but mutually incompatible.

| Architecture        | Extension |

|---------------------|-----------|

| Intel Pentium MMX   | MMX       |

| Intel Pentium III   | KNI/SSE   |

| AMD K6-2            | 3DNow!    |

| AMD Athlon          | 3DNow! 2  |

| Sun SPARC           | V9 VIS    |

| Motorola PowerPC G4 | AltiVec   |

| Digital Alpha       | MAX       |

| HP PA-RISC          | MAX       |

| MIPS                | MDMX      |

Table 3.2: Architectures with SWAR extensions.

<sup>&</sup>lt;sup>1</sup>Named "Sub-Word Parallelism" (SWP) in signal processing.

If we want to take advantage of these instructions sets this incompatibility makes it virtually impossible to write platform independent code by hand. And adapting a specific algorithm to a specific platform by hand is very timeconsuming. These leads to us to the question:

#### Can we automate this process?

I have only found one project, "The SWAR Homepage at Purdue University"<sup>2</sup>, which addresses this problem. They are developing a compiler (Scc) that inputs code in the form of the platform independent SWAR-extended C language "SWARC" and outputs code containing C language together with platform dependent macros and inline assembly. The output together with some include files<sup>3</sup> is, in turn, compiled to machine code using a C compiler and an assembler.

The project is aiming at supporting all of the platforms in Table 3.2 efficiently. All of these instruction sets are however mutually incompatible and some or many of the operations are not supported on some or any of the data types. Much of the effort is thus focused on the *code conversion problem*: how one can implement these missing operations using existing SWAR instructions or even conventional 32-bit integer functions. An efficient construction of such a general SWAR-compiler is therefore a very tricky task.

Scc can currently output SWAR-optimized code using either MMX, 3DNow!, generic IA-32 code or a combination of these. In the case of IA-32 code the compiler tries to use ordinary 32-bit integer functions when operating on sets of smaller sized integers. The compiler also supports parallel operations on integers with *arbitrary bit precision* (smaller than integer precision, though). The precision syntax is similar to C's bitfield syntax. As an example, the following piece of SWARC code

```

void add_8xS16(int:16 [8] z, int:16 [8] x, int:16 [8] y)

{

z = x + y;

}

```

specifies a function with three arguments. These are vectors of signed 16-bit integers each of length 8. We see that vector operations are easily expressed using the normal C operators such as +, -, \*, / etc. For further details, see SWARC's grammar which can be found in [2].

I tested the performance of the code generated by Scc compared to ordinary scalar C code. Three test operations, namely addition  $z_i = x_i + y_i$ , absolute value  $x_i = |y_i|$  and 11-norm  $z_i = |x_i| + |y_i|$  were applied to 16 elements long vectors of different sized signed integers. In order to make the execution times measurable each operation were run  $2^{20}$  times. The benchmarks can be seen in Table 3.3.

It is apparent that Scc generates fast code for simple operations that are easily expressible with target instructions, in this case MMX. But when it comes to implementing functions that are not e.g. 16-bit absolute value, the code generated is actually slower than the scalar C code. Consequently, Scc is currently only useful when optimizing simple vector operations for the Intel platform.

<sup>&</sup>lt;sup>2</sup>http://shay.ecn.purdue.edu/~swar/

<sup>&</sup>lt;sup>3</sup>Currently swartypes.h plus either Scc\_3dnow.h, Scc\_athlon.h, Scc\_max.h, Scc\_sse.h, Scc\_altivec.h, Scc\_ia32.h, Scc\_mmx.h or Scc\_xmmx.h

| Operation      | Precision | C                 | MMX               |

|----------------|-----------|-------------------|-------------------|

| Addition       | 8-bit     | $108 \mathrm{ms}$ | $45 \mathrm{ms}$  |

| Addition       | 16-bit    | $147 \mathrm{ms}$ | 56 ms             |

| Addition       | 32-bit    | $91 \mathrm{ms}$  | 98 ms             |

| Absolute value | 16-bit    | $269 \mathrm{ms}$ | 315 ms            |

| l1-norm        | 16-bit    | $521 \mathrm{ms}$ | $727 \mathrm{ms}$ |

Table 3.3: Performance difference between scalar C code and Scc-generated MMX-optimized code run on TS 1.

Scc's source code is available online as public domain in a testable alpha state. It is however not necessary to download Scc in order to use it because SWARC's website contains a test page<sup>4</sup> in which the visitor, through a HTML-form, can use the compiler. The output together with the appropriate include files can then be compiled using gcc. For the more interested reader, the webpage also links indepth articles that discuss the design of a the SWARC language [2] and its compiler Scc [3].

#### 3.8.2 SWAR in gcc

Not all operations are hard to hand-code using SWAR-operations, especially not if the GNU C Compiler gcc together with the GNU Assembler as are available on our target system. Here we can *express assembler instructions with arguments specified as C expressions.* This has several advantages:

- All the code belonging to an algorithm is placed together in the source code in an intuitive manner. No separate assembler files are needed.

- The programmer can concentrate on the relevant matters—which SWARinstructions that should be used, instead of bothering about how to set up the local function stack, push and pop registers, and other low-level assembler matters. This makes the overhead of programming in assembler minimal.

As an example, consider the two-dimensional affine transform

$$\mathbf{x} = \mathbf{A} \cdot \mathbf{x} + \mathbf{b}$$

where

$$\mathbf{x} = \begin{pmatrix} x_1 \\ x_2 \end{pmatrix}, \ \mathbf{A} = \begin{pmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{pmatrix}, \ \mathbf{b} = \begin{pmatrix} b_1 \\ b_2 \end{pmatrix}$$

This calculation can be implemented with 32-bits floating precision using 3DNow! instructions as follows

```

void f32_xAxb(f32_t *x, f32_t *A, f32_t *b)

{

```

| asm("movq | (%0), % | <b>%%</b> mmO | \n\t" | /* | x[0,1] | => | mmO | */ |

|-----------|---------|---------------|-------|----|--------|----|-----|----|

| "movq     | (%1), % | <b>%%</b> mm1 | \n\t" | /* | A[0,1] | => | mm1 | */ |

<sup>&</sup>lt;sup>4</sup>http://shay.ecn.purdue.edu/~swar/SccTest.html

```

"movq 8(%1), %%mm2 \n\t"

/* A[2,3] => mm2 */

(%2), %%mm3 \n\t"

/* b[0,1] => mm3 */

"movq

"pfmul %%mm0, %%mm1 n\t"

"pfacc %%mm1, %%mm1 \n\t"

/* first dot => mm1 */

"pfmul %%mm0, %%mm2 \n\t"

"pfacc %%mm2, %%mm2 \n\t"

/* second dot => mm2 */

"punpckldq %%mm2, %%mm1 \n\t" /* A*x

=> mm1 */

"pfadd %%mm3, %%mm1 \n\t"

/* A*x+b => mm1 */

"movq %%mm1, (%0) \n\t"

/* mm1

=> x */

\n\t"

"femms

/* cleaup mmx state */

/* out args to C */

: "r"(x), "r"(A), "r"(b) );

/* in args from C */

```

I compared this algorithm at the highest level of locality with a scalar version written in C. On TS 1 this gave a speedup factor of approx. 4.6.

For more information see the info pages on gcc. Currently the GNU Assembler supports the SIMD-instruction sets MMX, 3DNow! and 3DNow! 2.

#### 3.8.3 Trend

The current trend of PC processors is to add more SWAR-versions of the traditional scalar machine instructions addition, subtraction, multiplication and division. This means that gaps in the SWAR instructions sets are filled in which should make it easier to construct compilers that output efficient code. This is because less special cases, involving code conversion, need to be handled.

As an example, both the new PowerPC G4 and the next 64-bit Intel architecture (IA- $64^5$ ) will contain the very general *permutation* operation<sup>6</sup>. This will significantly speed up data conversion and other structure operations often used in signal and image processing and its implementation will be simple and easy to automate.

This trend of packing more instructions into processors is expected to continue. The main reason for this is that the transistor packing density in CPUs grows faster than their clock frequency. Assuming large data streams and parallel operations, a duplication of the instruction decoders theoretically doubles the performance of these SIMD-operations.

Viewed from a large perspective, this SWAR-trend actually means that RISC processors and DSPs are converging towards a single CPU. The most apparent example of this is the PowerPC G4.

## 3.9 Reconfigurable Computing

A totally different kind of computing category, which in the long run probably will become the *optimal solution* to the code conversion problem, is *reconfig*-

}

<sup>&</sup>lt;sup>5</sup>Currently code named "Itanium"

<sup>&</sup>lt;sup>6</sup>On the G4, this operation is capable of arbitrarily selecting data with the granularity of one byte from two 16-byte source registers into a single 16-byte destination register.

*urable computing.* These hardware technologies can, analogously with the learning process of the human brain, be adapted according to what operations that are to be performed. Because these reconfigurable hardwares are so general, *the code conversion process only has to be solved once for each programming language.* The software programmer, on the other hand, has to take more factors, such as minimal chip area and bit-level operations, into consideration during the design and optimization stages. This is outweighed by the fact that the code is very generic and long-lasting.

The basic technology consists of a silicon chip with a set of logical units that can be reprogrammed (reconfigured) each time a new set of functions is needed in the application, something that is called a Field-Programmable Device (FPD). The three main catogories of FPDs are delineated:

- Simple PLDs (SPLDs)

- Complex PLDs (CPLDs) and

- Field-Programmable Gate Arrays (FPGAs).

Of these, the FPGA has the highest capacity (measured in number of 2input NAND-gates) and is therefore the most commonly used when mapping more complex applications onto these kinds of logic. Under the right circumstances these circuits have a speed performance of *two orders of magnitudes* relative to that of CPUs [10]. They do not offer the same performance as Application Specific Integrated Circuits (ASICs) which, on the other hand, lack the possibility to be reprogrammed.

#### 3.9.1 Reconfigurable Applications

Image processing involves the analysis of very large amounts of data, with a high degree of parallelization possibilities in the algorithm and with a relatively low number of bits required per data element. Most arithmetic units on CPUs today are built for processing data with a precision of 32 or 64 bits. Because 16 bits precision often is enough when performing image processing, a lot of unneccessary processing is done on bits never used when using these CPUs.

When using FPGAs, on the other hand, both these two factors can be taken into consideration and utilized very effectively. For example, arithmetic operations can be specified on arbitrarily sized integers and several processing units of the same type can be configured to make use of the data parallelism.

One big disadvantage with this idea is that it means a lot of work for the programmer who has to redesign the algorithms for the operations to suit these further restrictions, especially the data precision issue. Therefore a high level programming environment which supports modular programming and reuse of code become important issues. Furthermore the FPGA-field is a relatively new and unexploited area in comparison to CPUs and their code development tools there are few libraries available to use. For further information see [10].

Programmable logic has also been successfully used in the development stages of new microelectronics and in some mixed computer architectures that make use of its unique benefits together with traditional microprocessors and random access memories. Most of the code on such a system is run on the traditional hardware except for the most time consuming parts that are small enough to fit onto the reconfigurable logic part, in this way using the best of both worlds. Also in this case we use the concept of locality to optimally fit hardware and software together. In these cases, the programmable circuits being used are often called FPGA-coprocessors. An example of such a system is the MATCH project, which will be covered next.

#### 3.9.2 Mixed Architectures

#### MATCH

The MATCH ("MATLAB compiler for heterogeneous computing systems") project is addressing the code conversion problem by trying to build a development environment that can overcome the barriers between low-level languages, especially C and VHDL (a hardware description language often used to describe FPGA designs), and the widely used high-level language MATLAB, suitable for the testing of numerical algorithms. As the word "heterogeneous" in the name implies, the target architectures consists of several different computing technologies, specifically a general-purpose CPU, a DSP and a FPGA board. The different parts are all good at different things and it is not apparent how the processing should be divided between the parts. The solution to this problem can be summarized in the following steps:

- 1. Parse the MATLAB code into a control and data flow graph (CDFG).

- 2. Partitioning this graph into sub-graphs that can be invidually mapped to different computer architectures in the target system. This step also involves the administration of buffer layouts and communication.

- 3. Finally generate the code for the different components and, in turn, use their respective compilers to produce the final object code that they understand.

The following list shows the project's eight main tasks in more detail together with their predicted efforts (in parenthesis).

- 1. Development of a hardware testbed (10%).

- 2. Implementation of MATLAB to C and VHDL compiler. (30%)

- 3. Automatic parallelism and mapping on heterogeneous resources while optimizing performance under resource constraints or vice versa. (15%)

- 4. Development of MATLAB compiler directives that specify type, shape, precision, data distribution and alignment, task mapping, resource and time constraints. (10%)

- 5. Evaluation of adaptive applications. (10%)

- Development of basic primitives such as FFT, FIR/IIR filtering, matrix addition and multiplication operations. (15%)

- 7. Development of interactive tools for function composition and logic synthesis. (5%)

### 3.9. RECONFIGURABLE COMPUTING

8. Development of faster algorithms for compilation, such as parallel or distributed algorithms for logic synthesis. (5%)

The MATCH project was initiated on Jun. 30, 1998 and is sponsored by NASA in order to be used in their upcoming space shuttles for earth observing systems. According to its planned milestones the project should, at the time of this writing, be finished and a demonstration is planned at the end of the first quarter 2001.

## Chapter 4

# **Implementation Aspects**

In this chapter we will discuss the different aspects we have to take into account when we turn from the ideal theoretical description of an algorithm to the description that is optimal in an environment with a specific programming language and computer architecture.

The focus is on general computer architectures, such as PC-systems, together with C or C++ as the software environment. On the MP-systems POSIX Threads are used to parallelize image processing operations.

## 4.1 **Programming Languages**

#### **4.1.1** MATLAB

MATLAB is, at an early stage in image processing research, a very handy language that enables quick implementation and testing of ideas. The machine precision of 64-bit floating point number is enough to cover most of the demands in our field. It is also quite fast if we can express our algorithms as matrix operations. But as MATLAB is an interpretive language, more complex operations involving lot of nested loops tend to run very slow. Another problem with MATLAB is its unpredictability in execution time because of its garbage collector. This also means that we have no explicit control of matrix buffers which in most cases is crucial for performance. The ability of MATLAB to express matrix operations in a high level notation is very convenient and it can also automatically generate C code or assembler code for different kinds of embeddable processors especially DSPs. But the test platform itself is best suitable for research, and not for running code in embedded systems.

#### 4.1.2 C and C++

My main approach is to implement image processing algorithms in different ways and then investigate the differences in performance and memory usage between these implementations. My target architecture are desktop computers because of their availability. Therefore C is a natural choice for me because of its great portability, performance possibilities to investigate low-level aspects of operations. For more complex projects, higher level languages such as C++ or Java would be to prefer. As these are based on C, porting the code should not be a big effort. If needed, it is also possible to call functions in C-coded object files from either C++ or Java.

Because of its free and open development environment and because of my earlier experince with Linux, I chose to develop all the code on a PC Linux system using the C and the C++ compiler in the GNU Compiler Collection, also known as GCC<sup>1</sup> This compiler is well-known for its high performance and large target support<sup>2</sup>. All code was compiled with the switch -O6, which certifies maximum speed optimization in current and upcoming versions of GCC.

## 4.2 Matrix Storage Techniques

#### 4.2.1 Matrix Elements

Computers are designed to efficiently operate on rectangular regions and most images are digitized using a regular sampling grid. Thus, the storage techniques I will discuss are all based on the assumption that the elements together form a rectangular region of data. A row and a column is regarded as a special case of such a rectangle.

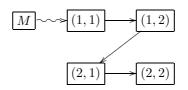

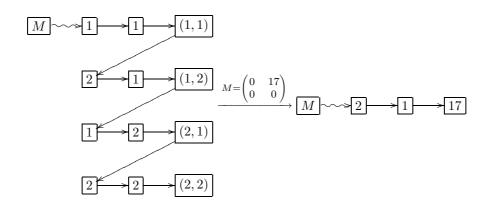

To accompany the textual explanations I have added a graphical explanation for each technique that is discussed. These can be viewed in the Figures 4.1, 4.2, 4.3 and 4.4. In these a curly arrow shows a pointer dereference and its direction. The straight arrows, on the other hand, indicate in what order the matrix elements, drawn as boxes, are stored in memory. The actual matrix position of such an element is expressed using double indexing (x, y), starting at (1, 1).

#### Dense

The simplest and most straightforward way of storing a matrix in memory is to allocate one whole continuos memory block containing all the elements of the matrix. Such a matrix is said to be *dense*. A densly stored matrix is illustrated in Figure 4.1. In image processing the elements are normally stored like we read a text—*row-major*, left-to-right, starting with the first row. This is also called *lexicographic* order. In the following we assume that all dense matrices are stored in this order.

#### **Row-Indexed Dense**

When we access a matrix element with index (x, y) in a density stored matrix, having the width w and height h, we perform the calculation  $i = x + y \cdot w$  to

<sup>&</sup>lt;sup>1</sup>GCC also contains front-ends for, Objective C, Chill, Fortran, and Java (GCJ) giving us great possibilities to mix different languages in the same project. Note that GCJ compiles Java source code to machine code, and is not a Java virtual machine.. For more information see http://gcc.gnu.org/

<sup>&</sup>lt;sup>2</sup>Currently GCC supports alpha-dec-linux, alpha-dec-osf, DOS, hppa-hp-hpux, hppa-hp-hpux9, hppa-hp-hpux10, hppa-hp-hpux11, i386-linux, i386-sco3.2v5, i386-solaris, i386-udk, i386-ibm-aix, m68k-nextstep, m68k-sun-sunos4.1.1, mips-sgi-irix, mips-sgi-irix6, powerpc-linux-gnu, powerpc-solaris, sparc-sun-solaris, sparc-sun-solaris2.7, sparc-sun-sunos, GCC with Windows or OS/2.

Figure 4.1: Dense storage of a  $2 \times 2$ -matrix.

get the linear index. By using this index together with the start address of the matrix we can then reach our element.

Sometimes the multiplication  $y \cdot w$  can be costly and in these situations we allocate an additional vector containing the memory addresses to the starts of the rows in the matrix. This adds an extra pointer dereference for each new row that is to be read but on the other hand eliminates an integer multiplication. I will call these matrices row-indexed dense matrices (RID-matrices). An example of such a matrix is illustrated in Figure 4.2.

Figure 4.2: Dense storage of a  $2 \times 2$  using row-indexes.

#### Tiled Dense