### UNIVERSITÉ DE MONTRÉAL

# CONTINUOUS/DISCRETE CO-SIMULATION INTERFACES FROM FORMALIZATION TO IMPLEMENTATION

# LUIZA GHEORGHE DÉPARTEMENT DE GÉNIE INFORMATIQUE ET GÉNIE LOGICIEL ÉCOLE POLYTECHNIQUE DE MONTRÉAL

### **THÈSE**

PRÉSENTÉE EN VUE DE L'OBTENTION

DU DIPLÔME DE PHILOSOPHIÆ DOCTOR (Ph.D.)

(GÉNIE INFORMATIQUE)

AOÛT 2009

### UNIVERSITÉ DE MONTRÉAL

### ÉCOLE POLYTECHNIQUE DE MONTRÉAL

#### Cette thèse intitulée:

# CONTINUOUS/DISCRETE CO-SIMULATION INTERFACES FROM FORMALIZATION TO IMPLEMENTATION

présentée par: **GHEORGHE Luiza**

en vue de l'obtention du diplôme de : <u>Philosophiæ Doctor</u> a été dûment accepté par le jury d'examen constitué de :

M. QUINTERO Alejandro, Doct., président

Mme. NICOLESCU Gabriela, Doct., membre et directrice de recherche

M. AIT MOHAMED Otmane, Ph. D., membre

M. VANGHELUWE Hans, Ph. D., membre

# **DEDICATION**

To my family

#### **ACKNOWLEDGMENTS**

There are many generous people that made this work possible and to whom I want to express my most heartfelt appreciation

My warmest thanks go to Mrs. Gabriela Nicolescu, my advisor, for her trust and support during all these years. To her I owe a great debt of gratitude for the advices, the confidence and the encouragement that helped me along the way. She has been a model adviser, patient and genuinely collaborative. Without her example I would not be where I am today.

Special thanks go to Mrs. Hanifa Boucheneb for her help, her advices and her selfless availability. Thank you for helping me discover the world of abstractions and formal representations.

I want to thank to Mr. Alejandro Quintero, Mr. Otmane Ait Mohammed, Mr. Hans Vangheluwe and Mr. Christian Cardinal for accepting to be part of the jury.

I also want to thank the ones that believed in me and helped me fulfill one of my dreams, that of teaching; Mrs. Gabriela Nicolescu, Mr. Guillaume-Alexandre Bilodeau and Mr. Pierre Langlois my most sincere appreciation

I would also like to thank Mr. Ahmed Amine Jerraya, at the time head of SLS at TIMA laboratory, for welcoming me in their group. Even though the time spent there was very short, it was rich in information and knowledge.

A very special note of gratitude goes to Mr. Ian O'Connor – his work, his advancements brought me to discover and helped me become interested in optical networks on chip.

The "Conseil de recherches en sciences naturelles et en genie du Canada" (CRSNG) was very generous in providing me with scholarship assistance – thank you.

I want to mention my lab colleagues with whom I shared the lab and with whom I worked with on different projects: Maimouna, Bruno, Alain, Taieb, Sebastien, Matthieu, Essaid, Youcef and Faouzi. Thank you! It was a great privilege to have met and worked with you and I hope our paths will meet in the future professionally and otherwise.

I would also like to thank my friends Ana, Vinnie and Joachim for understanding my busy working schedule and therefore not being able to meet them when we wanted. Thank you, guys!

And last but not least I would like to thank my family for putting up with me: my son Alex, for being, my husband Michael for being so understanding and my mother who gave me the discipline to go through difficult times, all of them have been very supportive of my studies and my work. I only wish my father was still with us and could be happy for me, however his life is always a beacon for me now and in the future, may he rest in peace.

Thank you all and I sincerely apologize to anyone I have left out or omitted inadvertently.

#### **ABSTRACT**

Today's systems-on-chip are growing in complexity as a result of a higher density of components on the same chip, and also on account of the heterogeneity of different modules that are particular to different application domains (i.e. mechanical, electrical, optical, biological and chemical). These systems can be found in a broad and diverse spectrum of applications in many industries, including but not limited to Automotive, Aerospace, Health Care and, Consumer Electronics. These multi-domain heterogeneous systems enable new applications and the creation of new markets. This thesis focuses on the design and the simulation of heterogeneous embedded systems, more specifically on continuous/discrete heterogeneous systems.

Continuous-time and discrete-event models are at the core of the design of multi-domain systems. We present here a generic, language independent methodology for the design of continuous/discrete heterogeneous systems. This methodology is the basis for design of a new framework providing the interfaces that are in charge with the heterogeneous components adaptation. The methodology was successfully used for the implementation of different continuous/discrete systems such as: a glycemia level regulator, an analog/digital converter, a PID controller, a production chain control system and wimax system.

Parts of the proposed methodology were adapted for the formalization, modeling and verification of an optical network on chip.

### **RÉSUMÉ**

Les systèmes sur puce sont de plus en plus complexes, pas seulement en terme de densité de composants sur la même puce mais aussi en terme d'hétérogénéité des modules spécifiques pour différents domaines d'application (mécanique, électrique, optique, biologique chimique). On retrouve ces systèmes dans un grand éventail d'applications et dans divers industries tels que l'automobile, l'aéronautique, la santé, l'électroniques et autres. Ces systèmes hétérogènes multi-domaine permettent de nouvelles applications et la création de nouveaux marchés. Cette thèse se concentre sur la conception et la simulation des systèmes hétérogènes embarqués.

Les modèles temps-continu et événement discret sont le noyau de la conception des systèmes multi-domaine. On présente ici l'analyse de modèles d'exécution et modèles de synchronisation des systèmes hétérogènes continu/discret, la définition d'une méthodologie générique pour la conception des outils de co-simulation des systèmes hétérogènes continus/discrets et la validation de la méthodologie par applications – la réalisation d'un cadre de co-simulation pour les systèmes continu/discret. La méthodologie exploite les techniques de vérification formelle et de la simulation. La conception des outils de simulation est basée sur la définition d'une architecture générique des interfaces de simulation ainsi que sur des modèles de synchronisation vérifiés formellement. La méthodologie a été utilisée pour l'implémentation d'un régulateur de niveau de glycémie. Une partie de la méthodologie a été adaptée pour la formalisation, la modélisation et la vérification formelle d'un réseau optique sur puce.

# CONDENSÉ EN FRANÇAIS

Les systèmes sur puce sont de plus en plus complexes, pas seulement en terme de densité de composants sur la même puce mais aussi en terme d'hétérogénéité des modules spécifiques pour différents domaines d'application (mécanique, électrique, optique, biologique chimique). On retrouve ces systèmes dans un grand éventail d'applications et dans divers industries tels que l'automobile, l'aéronautique, le médical, l'électroniques et autres. Ces systèmes hétérogènes multi-domaine permettent de nouvelles applications et la création de nouveaux marchés. Les modèles temps-continu et événement discret sont le noyau de la conception des systèmes multi-domaine. Ce projet s'articule autour d'un point clé pour la conception des systèmes continus/discrets (C/D): la conception à partir d'un niveau haut d'abstraction. Le projet propose une méthodologie indépendante des langages de programmation qui permet la conception efficace des outils de co-simulation pour tels systèmes. La méthodologie a été utilisée pour la conception d'un nouveau cadre qui fournit des interfaces en charge avec l'adaptation des composants hétérogènes. Ce cadre a été utilisé pour l'implémentation d'un régulateur de niveau de glycémie.

# 1. Problématique

L'intégration des composants hétérogènes à un niveau élevé d'abstraction nécessite un nouveau cadre conceptuel pour l'abstraction des différentes interfaces qui réalisent l'adaptation entre les composants hétérogènes ainsi que des nouvelles méthodologies pour la validation. L'hétérogénéité implique l'utilisation des modèles en temps continu ainsi que des modèles à événements discrets dans un modèle globale, donnant une vue d'ensemble du système. Étant donnée l'hétérogénéité des concepts manipulés par ces deux types de modèles, la validation globale demande des interfaces de simulation capables de fournir des modèles de synchronisation qui peuvent accommoder le domaine continu et le domaine discret. Dans le cas des outils de validation plusieurs sémantiques d'exécution doivent être prises en considération pour réaliser la simulation

globale. La technique de validation la plus souvent utilisée est la co-simulation. La co-simulation permet l'exécution concurrente des différents simulateurs en parallèle. Cette validation élimine la détection tardive des erreurs et réduit le temps de conception. Il est donc nécessaire de définir un modèle d'exécution globale dont les éléments de base sont :

- les *modèles* des composants du système hétérogène qui sont décrits en temps continu ou bien dans le domaine des événements discrets

- les *interfaces de co-simulation* qui réalisent l'adaptation de chaque modèle au bus de co-simulation, l'adaptation des différents protocoles de communication et la synchronisation entre les deux modèles.

- le *bus de co-simulation* qui est responsable de l'interprétation des interconnections entre les deux modèles composant le modèle global.

Les aspects qui rendent difficile la modélisation et la simulation des systèmes continus/discrets sont [6]:

- pour le modèle discret *le temps* est une notion globale pour tous les modules du système, il avance discrètement en passant par les instants discrets définis par les temps de notification des événements discrets. Pour le modèle continu le temps est une variable globale qui avance par le temps d'intégration (continu ou variable);

- pour le modèle discret *les processus* sont sensibles aux événements alors que, pour le modèle continu, les processus sont exécutés à chaque pas d'intégration;

- pour le modèle discret *la communication* est réalisée par ensembles d'événements alors que pour le modèle continu, la communication est réalisée par des signaux continus (un signal continu possède une valeur à touts instants);

- chaque modèle doit être capable de *détecter*, de *localiser* en temps et de *réagir* aux *événements* envoyés par l'autre modèle.

La conception des interfaces de co-simulation est couteuse en termes de temps, est une source d'erreurs, est difficile à déboguer, influence les performances de la simulation

globale et demande la compréhension exhaustive des simulateurs impliqués dans la cosimulation. La clé de voûte consiste donc en la définition rigoureuse du comportement et de l'architecture des interfaces de co-simulation pour la génération automatique.

Le modèle formel qui est la représentation abstraite, rigoureuse d'un modèle, représente la base de la définition d'un outil générique de co-simulation qui fournit des modèles globaux de co-simulation pour la validation des systèmes hétérogènes continus/discrets. En représentant le modèle formel tous les requis du système sont précisément définis et toutes les inconsistances et les ambigüités sont éliminées.

### 1.1 Objectives et contributions

Les objectifs du travail présenté ici sont :

- la définition d'une approche pour la conception des outils de validation efficaces pour les systèmes hétérogènes

- l'intégration, dans l'étape de validation, de nouveaux aspects spécifiques pour la nouvelle génération de systèmes hétérogènes multi-domaine : l'interaction entre le modèle continu et le modèle discret

Les contributions plus spécifiques sont :

- l'analyse de modèles d'exécution et modèles de synchronisation des systèmes hétérogènes continu/discret

- la définition d'une méthodologie générique pour la conception des outils de cosimulation des systèmes hétérogènes continus/discrets.

- la validation de la méthodologie par applications la réalisation d'un cadre de co-simulation pour les systèmes continu/discret, l'implémentation d'un régulateur de glycémie et la modélisation et la vérification formelle d'un réseau optique passif, sur puce.

### 2. Revue de littérature

Cette section est un survol de travaux existants. Ces travaux peuvent être divisés en deux catégories : une basée sur la simulation et une basée sur la représentation formelle. Dans la première catégorie il existe deux approches pour réaliser la co-simulation des systèmes hétérogènes : une approche homogène et une approche hétérogène ([5]):

- L'approche *homogène* où les concepteurs utilisent un seul langage pour la spécification complète du fonctionnement du système et donc les descriptions des diverses parties sont réalisés dans un langage unique de simulation (tel que le C pour accélérer les simulations) ([9], [10], [11],, [12] [13], [14], [15]) La difficulté est d'être assuré que la traduction et la simulation du langage unique ne change pas la sémantique des descriptions des diverses parties.

- L'approche *hétérogène* ou les concepteurs utilisent des langages spécifiques pour la modélisation des différents modules d'un système complet et donc ils conservent les descriptions spécifiques des diverses parties et exécutent en parallèle les divers simulateurs ([18], [19], [20]). La communication et la synchronisation entre simulateurs sont assurées par le bus de co-simulation. Cette tache peut être difficile lorsque les modèles de simulation sont différents.

Ayant la description informelle du système, il est nécessaire d'avoir la description du modèle dans une forme abstraite de spécification à base de règles. Cette forme caractérise le modèle dans un langage mathématique, celui de la théorie des ensembles ou de la théorie des systèmes ou un autre paradigme formalisé [4].

Dans les domaines des définitions formelles et du formalisme, on peut énumérer les travaux de :

- l'Université de Berkeley [25] ou les auteurs proposent un cadre formel pour la comparaison de plusieurs MoCs;

- « Royal Institute of Technology » de Stockholm [26], [27]ou l'auteur a proposé un cadre formel qui sépare les aspects de communication /synchronisation et le

comportement interne. Un processus est divisé en deux parties : le noyau du processus qui est responsable du calcul et l'enveloppe (de l'anglais « shell ») du processus en charge de la communication avec les autres processus;

- l'Université d'Arizona [28], [29] ou les auteurs définissent un formalisme mathématique DEVS pour la spécification d'un système. Ce formalisme est une représentation d'un système à « entrée-sortie » ayant une base de temps réel et continu. Des travaux sur les modèles ou le système discret retourne en arrière sont présentées dans [35] [36], [37] et [38].

Les travaux basés sur la simulation, l'approche homogène sont couteux en termes de temps de développent des nouvelles bibliothèques de composants et temps d'apprentissage pour les développeurs qui travaillent avec les outils. Dans le cas des travaux basés sur la simulation, l'approche hétérogène les interfaces sont conçues adhoc, ne sont pas vérifies formellement et ne se concentrent pas sur les domaines continu et discret. Cette thèse propose une approche ou les développeurs travaillent avec des outils très populaires et peuvent réutiliser des modèles qui existent dans des bibliothèques déjà testées. Les interfaces sont vérifiées formellement et sont générées automatiquement.

Les travaux basés sur la représentation formelle fournissent une base abstraite pour les systèmes hétérogènes mais ils ne prennent pas en considération les interfaces de cosimulation ou ils ne permettent pas la vérification formelle. Cette thèse se concentre sur les interfaces de co-simulation et donne un mécanisme pour la représentation formelle et la vérification formelle des interfaces de co-simulation,

# 3. Concepts de base

Cette section introduit les concepts de base qui seront utilisés dans ce travail : les modèles d'exécution et les simulateurs continu et discret, le modèle de synchronisation ainsi que la définition de l'environnement de simulation continu/discret.

### 3.1 Modèles d'exécution

#### 3.1.1 Modèle à événements discrets

La simulation d'un modèle purement discret est basée sur les événements, elle est généralement accomplie en utilisant un simulateur à événements discrets. Le rôle de simulateur est de maintenir l'ordre des événements dans une file d'attente suivant leur temps de notification. A chaque itération, le simulateur fait sortir de la file l'événement qui a le temps de notification le plus proche et exécute les processus sensibles à cet événement. L'exécution de ces processus peut générer d'autres événements entraînant l'exécution d'autre processus. Si les événements dont le temps de notification égale au temps actuel sont tous traités, le simulateur avance le temps pour le plus proche événement planifié.

#### 3.1.2 Modèle en temps continu

La simulation d'un modèle purement continu régi par des équations différentielles et algébriques est basée sur la résolution numérique de ces équations. La plupart des algorithmes de résolution discrétisent le temps en un ensemble d'instants. La différence entre deux instants est appelée *pas d'intégration* ou pas de calcul et suivant l'algorithme utilisé ce pas peut être fixe ou variable. Les critères utilisés pour le choix du pas d'intégration sont : la précision, la stabilité et la continuité des signaux. Dans les cas où la précision est la seule condition (le cas ou le modèle est stable et il n'y a pas de discontinuités), il est possible d'utiliser un algorithme à pas fixe. L'utilisation d'un algorithme à pas variable augmente les performances de simulation. Pour satisfaire les critères de précision l'algorithme réduit le pas quand le modèle évolue rapidement. Pour éviter les calculs qui ne sont pas nécessaires et améliorer la vitesse de simulation l'algorithme augmente le pas quand le modèle évolue lentement,.

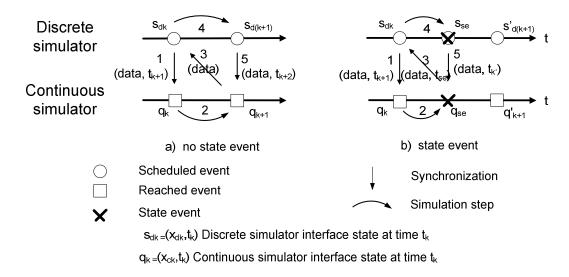

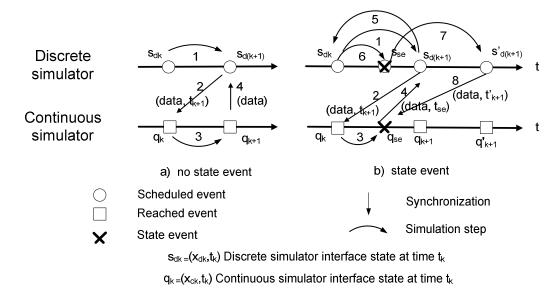

Pour une synchronisation rigoureuse, chaque simulateur impliqué dans la co-simulation C/D doit considérer les événements provenant de l'environnement externe. Ils doivent

s'arrêter avec précision aux échantillons de temps de ces événements (détection des événements). Ces échantillons de temps sont des points de communication entre les deux simulateurs.

Le simulateur continu doit détecter le prochain événement discret planifié par le simulateur discret. Cette détection implique l'ajustement des pas d'intégration pour le simulateur continu. Le simulateur discret doit détecter les événements d'état. Un événement d'état est un événement non prédictible qui est généré par le simulateur continu et qui a une estampille de temps dépendante des valeurs des variables d'état (comme par exemple les événements « passage a zéro » ou le dépassement d'un seuil). La conséquence est le contrôle de l'avancement en temps des simulateurs discrets (au lieu d'avancer le pas de simulation prévu, le simulateur avance précisément jusqu'au moment de l'évènement d'état).

### 3.2 Modèles de synchronisation

Table 1. Modèles de synchronisation

| Modèle de synchronisation                                    | Pas de synchronisation                                                                               | Avantages                                                                                                                                   | Désavantages                                                                                                       |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| Le modèle canonique                                          | A chaque pas<br>discret et chaque<br>occurrence d'un<br>événement                                    | Général                                                                                                                                     | Surdébit de synchronisation                                                                                        |  |

| Le modèle de<br>synchronisation<br>avec retour en<br>arrière | A chaque occurrence des événements de mise à jour, événements d'échantillonnage et événements d'état | Evénements de mise à jour, événements d'échantillonn age non-périodiques, efficace si le modèle continu ne génère pas des événements d'état | Retour en arrière pour<br>le modèle discret est<br>requis ci le modèle<br>continu génère des<br>événements d'état. |  |

Ce projet est basé sur deux modèles de synchronisation :

- le modèle canonique ou le simulateur continu avance le temps avant le simulateur discret.

- le modèle de synchronisation avec retour en arrière (« rollback » en anglais) ou le simulateur discret avance le temps avant le simulateur continu.

Le Table 1 montre les deux modèles de synchronisation comparés de point de vue pas de synchronisation ainsi que leurs avantages et désavantages.

# 4. Méthodologie de conception des outils de co-simulation

Cette section présente notre approche pour la spécification et la simulation des systèmes hétérogènes continus/discrets. L'accent sera mis sur les interfaces de simulation et leur génération automatique, le bus de co-simulation, ainsi que sur la communication et la synchronisation entre le deux modèles.

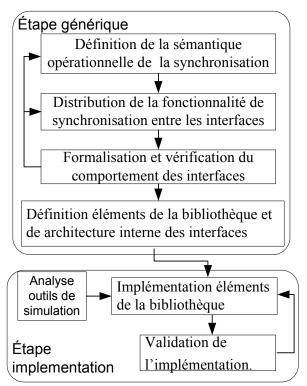

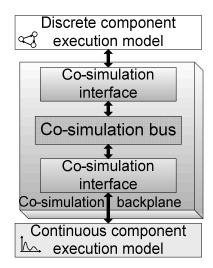

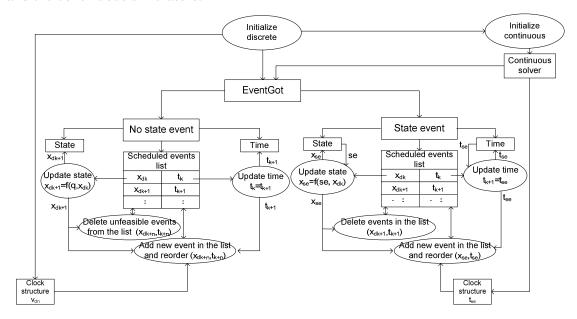

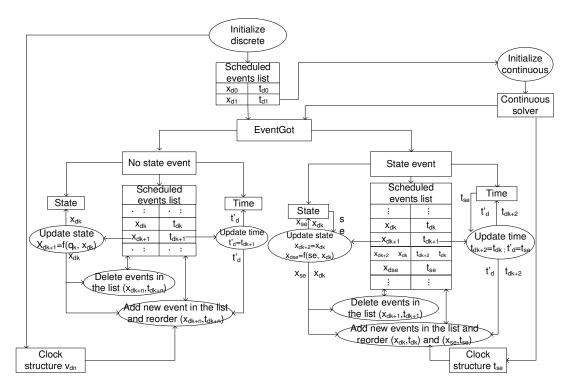

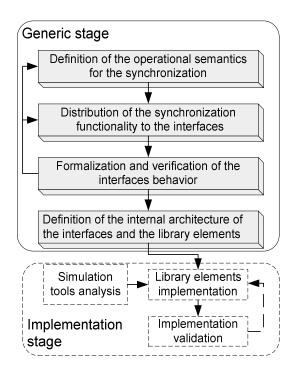

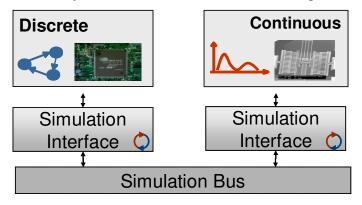

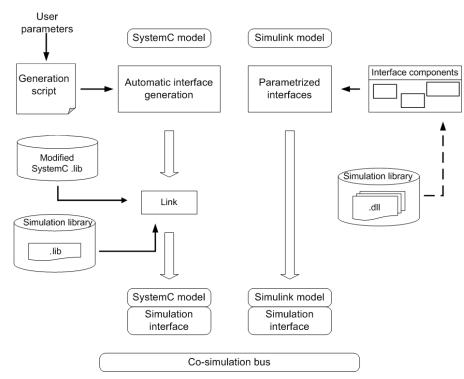

Pour permettre la conception des outils de co-simulation, la méthodologie qu'on propose est formée de deux étapes indépendantes des outils de co-simulation utilisés pour simuler le modèle continu et le modèle discret (voir Figure 1). Pendant ces étapes les interfaces de co-simulation sont définies dans un cadre conceptuel, leurs fonctionnalités et l'architecture interne sont décrites à l'aide des formalismes existants et logique temporelle.

Les deux étapes sont:

- 1. L'étape générique incluant les tâches suivantes:

- Définition de la sémantique opérationnelle des modèles de synchronisation pour le modèle global de co-simulation.

- Distribution de la fonctionnalité de synchronisation entre les interfaces de cosimulation.

- Formalisation et vérification du comportement des interfaces de co-simulation.

- Définition des éléments de la bibliothèque et l'architecture interne des interfaces de co-simulation.

- 2. L'étape d'implémentation incluant les tâches suivantes:

- L'analyse des outils de simulation pour les intégrer dans le cadre de cosimulation.

- L'implémentation des éléments spécifiques de la bibliothèque et validation de l'implémentation.

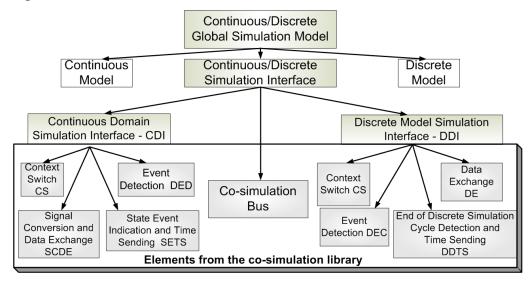

Figure 1. Méthodologie générique pour la conception des outils de co-simulation Les tâches de l'étape générique sont détaillées dans les sous-sections suivantes.

# 4.1 Définition de la sémantique opérationnelle des modèles de synchronisation pour le modèle global de co-simulation

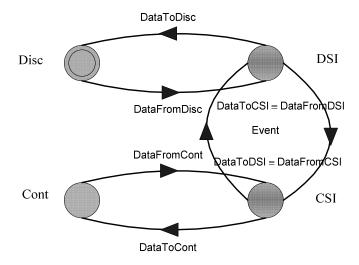

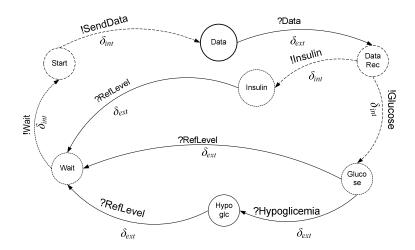

La sémantique opérationnelle est la représentation du comportement du système dans une forme mathématique, rigoureuse, non-ambigüe. Ce modèle sert comme base pour l'analyse et la vérification. Dans notre travail, pour définir la sémantique opérationnelle, sous forme de règles, on a utilisée le formalisme proposé par [28], [29] – Discrete Event System Specifications (DEVS). Nous avons définit la sémantique opérationnelle des deux modèles de synchronisation présentés dans la section 3.2.

# **4.2** Distribution de la fonctionnalité de synchronisation entre les interfaces de co-simulation

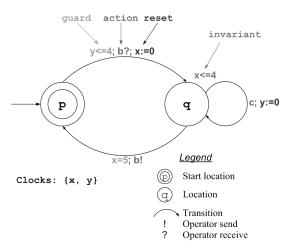

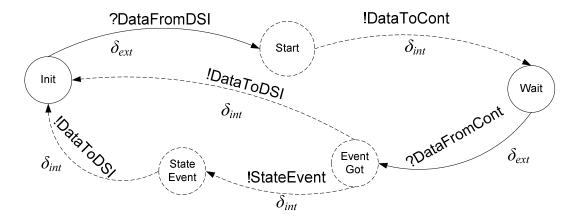

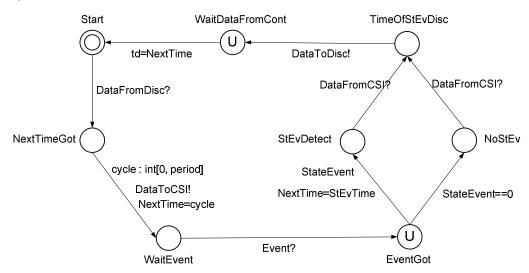

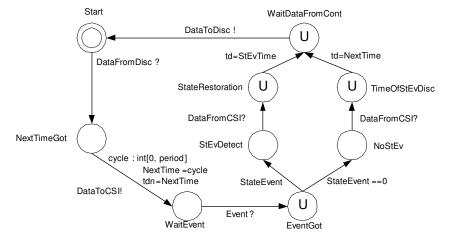

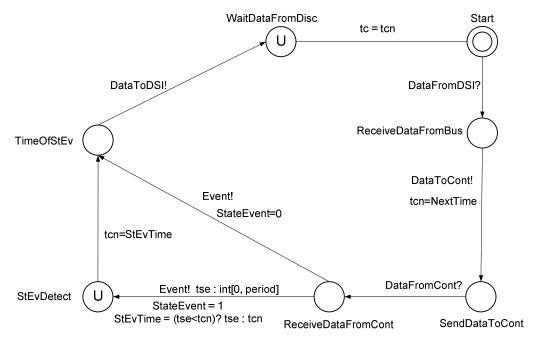

Apres la sémantique opérationnelle, la fonctionnalité de la synchronisation est distribuée entre les interfaces de co-simulation. Le premier pas de cette opération consiste en l'identification de la sémantique opérationnelle de chaque interface, à partir de la sémantique globale. La fonctionnalité de chaque interface a été par la suite modélisée à l'aide des automates temporisés.

# 4.3 Formalisation et vérification du comportement des interfaces de co-simulation

La formalisation et vérification formelle des interfaces de co-simulation peut être divisée en trois pas : la représentation formelle, la simulation du modèle formel et la vérification formelle. Pour réaliser cette étape on a utilisé les automates temporisés ([46], [47]) et l'outil UPPAAL ([48]).

# 4.4 Définition des éléments de la bibliothèque et l'architecture interne des interfaces de co-simulation

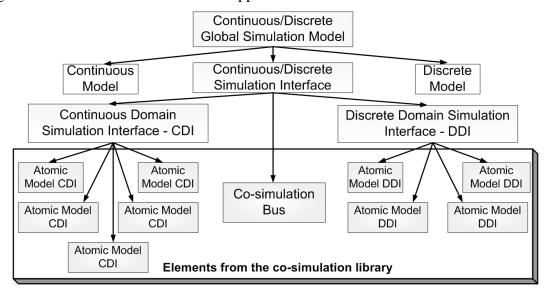

La vérification formelle du comportement des interfaces est suivie par la définition de l'architecture interne des interfaces de co-simulation. Cette définition est une étape clé pour la génération automatique des interfaces de co-simulation. Dans notre approche les interfaces ont été représentées comme un ensemble de modules hiérarchiques, en se basant sur des composants atomiques qui sont des éléments de la bibliothèque utilisée pour la génération automatique.

# 4.5 L'analyse des outils de simulation pour les intégrer dans le cadre de co-simulation

Des fonctionnalités spécifiques sont demandées pour les simulateurs continu et discret et donc l'intégration des outils de simulation dans l'environnement de co-simulation demande l'analyse des outils de simulation. Le simulateur continu doit détecter les événements d'état, il doit envoyer des données pour la synchronisation vers le modèle discret, permette des points d'interruption pendant la résolution des équations différentielles et la mise à jour des points d'interruption. Le modèle discret doit détecter la fin du cycle de simulation, doit permettre l'ajout/l'extraction de nouveaux éventements dans/de la queue de l'ordonnanceur et doit envoyer les résultats du traitement des données et l'information pour la synchronisation vers le simulateur continu.

# 4.6 L'implémentation des éléments spécifiques de la bibliothèque et validation de l'implémentation

Le dernier pas de la méthodologie est l'implémentation des éléments spécifiques de la bibliothèque et validation de l'implémentation. Cette étape dépend des outils de simulation choisis dans l'étape précédente, l'analyse des outils de simulation.

### 5. Résultats

A partir de la méthodologie présentée dans la section 3, l'outil de de co-simulation CODIS a été créé. Cet outil permet la modélisation et la simulation précise d'un système continu/discret. Les entrées dans le flot de simulation sont :

- le modèle continu (en Simulink® [16]) qui est schématique

- le modèle discret (en SystemC [8]) qui est textuel.

La sortie du flot est le modèle global de simulation. Les interfaces de co-simulation sont automatiquement générées par un générateur des interfaces qui reçoit à l'entrée des

paramètres définis par utilisateur via un générateur de script. À la sortie on obtient le modèle discret avec ses interfaces de simulation. Plus des détails sur CODIS peuvent être trouvées dans l'annexe 2 ([51], [52]). L'outil CODIS a été utilisé pour valider plusieurs applications, parmi eux, un régulateur de niveau de glycémie. Un régulateur de niveau de glycémie est un système qui représente une alternative pratique au traitement classique du diabète de type 1. Une technique plus avancée est la thérapie par pompe, un traitement qui fournit au corps insuline ou glucose en se basant sur les valeurs en temps réel de la glycémie. Cette application consiste dans la simulation d'un régulateur de niveau de glycémie. Le système est formé par deux sous-systèmes – un sous-système discret qui contrôle l'injection et un sous-système continu qui modélise le système d'injections, le patient et l'assimilation de glucose et insuline dans le sang.

# 6. Réseaux optiques sur puce

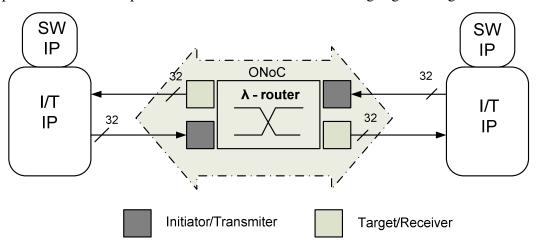

Dans cette partie on présente des résultats ou le formalisme et la vérification formelle sont appliqués pour la formalisation, la modélisation et la vérification d'un système hétérogène, un réseau optique sur puce. Ces résultats qui sont des résultats complémentaires, ou une partie de la méthodologie proposée a été appliquée sont présentés dans l'annexe 1.

Les systèmes modernes sur puce intègrent plusieurs composants hétérogènes comme différents processeurs, composants matériel et interconnexions complexes qui utilisent différents protocoles de communication. Les interconnections sur puce sont limitatifs de point de vue performance et consommation d'énergie. La croissance, en termes de nombre, des composants intégrés sur une puce augmente l'impact des effets comme le bruit causé par la diaphonie, les interférences électromagnétiques qui peuvent produire des erreurs de données, les délais et autres [56]. Les réseaux optiques sur puce s'avèrent une solution intéressante. Parmi les avantages des réseaux optiques on peut mentionner : extensibilité, simplicité, surface réduite, guide d'ondes bidirectionnel, réduction de la diaphonie, charge capacitive, et de la distorsion du signal, débit élevé dans le guide

d'ondes. Les défis les plus importants sont l'accès au prototypage physique et la difficulté d'influencer les processus standard existants. Par conséquence, la modélisation et la simulation deviennent une alternative nécessaire pour l'exploration de ces systèmes. Plus des détails sur les concepts de base des réseaux optiques sur puce peuvent être trouvés dans l'annexe 2 de ce document.

Une partie de la méthodologie proposée dans ce travail a été utilisée pour aider les concepteurs à réaliser des modèles complexes de tels systèmes. Dans ce document on a proposé: la formalisation des interfaces opto-électriques a l'aide du formalisme DEVS<sup>1</sup>, la formalisation des éléments passives de base composant un réseau optique<sup>1</sup> et la modélisation et la vérification formelle, pour la validation globale du comportement d'un réseau optique passif sur puce.

# 7. Conclusions et perspectives

Cette thèse se concentre sur la conception et la simulation des systèmes hétérogènes embarqués, plus spécifiquement sur les systèmes multi-domaine ou plusieurs composants de différents domaines comme optique, électrique, mécanique, sont pris en considération.

<sup>1</sup> Ce travail a été réalisé en collaboration avec Ph.D Mathieu Brière et Prof. Dr. Ian O'Connor, École Centrale de Lyon, France

#### 7.1 Conclusion

Cette recherche a été motivée par le contexte courant des systèmes embarqués. On retrouve ces systèmes dans un grand éventail d'applications et dans divers industries tels que l'automobile, l'aéronautique, la santé, l'électroniques et autres. Ces systèmes hétérogènes multi-domaine permettent de nouvelles applications et la création de nouveaux marchés. Les modèles temps continu et événements discrets sont la base des systèmes multi-domaine. Ce travail cible les systèmes hétérogènes continu/discret, plus spécifiquement la conception d'un nouveau cadre qui fournit des interfaces de simulation en charge avec l'adaptation de divers simulateurs.

Un sommaire des contributions majeures est présenté ci-dessous :

- l'analyse des modèles d'exécution des systèmes continus et discrets et la définition des modèles d'exécution globaux basés sur deux modèles de synchronisation

- la définition d'une méthodologie générique pour la conception des outils de cosimulation des systèmes hétérogènes C/D. La méthodologie comporte deux étapes :

- une étape générique ou la représentation des interfaces est raffinée d'un modèle de synchronisation abstraite jusqu'à l'architecture interne des interfaces de co-simulation

- une étape d'implémentation

- la validation de la méthodologie par applications la réalisation d'un cadre de co-simulation pour les systèmes C/D, l'implémentation d'un régulateur de glycémie et la modélisation et la vérification formelle d'un réseau optique passif, sur puce.

### 7.2 Perspectives

Cette thèse fait des progrès dans le développent d'une technique vérifiée pour la conception d'outils de co-simulation des systèmes hétérogènes continu/discret et ouvre des nouvelles directions pour les chercheurs qui travaillent dans la simulation au niveau système. La méthodologie proposée permet de nouveaux développements dans la génération automatique des interfaces de co-simulation pour les systèmes hétérogènes continu/discrets. Une nouvelle direction de recherche ouverte par ce travail est la vérification formelle de la composition des éléments de bibliothèque pour créer une interface. Une autre direction est l'analyse des modèles continus et discrets a intégrer pour vérifier la compatibilité en termes d'entrées, de sorties et de niveaux d'abstraction. Ce travail peut être continué avec la modélisation et la simulation des systèmes hétérogènes C/D aux différents niveaux d'abstraction et l'intégration du modèle de synchronisation avec retour en arrière dans l'outil de co-simulation proposé. Autres outils spécifiques pour le domaine discret peuvent être intégrés pour valider le travail (i.e SystemVerilog). Du travail peut être fait pour l'analyse de performance et l'optimisation des systèmes.

Un autre domaine dans lequel le travail présenté peut être exploité est la modélisation et la validation des réseaux optiques sur puce. Une direction pour les travaux futurs pourrait être l'intégration des composants optiques passifs et actifs avec des circuits intégrés, pour réaliser le modèle global d'exécution d'un réseau optique sur puce. A plus long terme, les interconnexions optiques peuvent être intégrées avec plusieurs processeurs sur la même puce et la méthodologie proposée peut être adaptée pour la modélisation et la validation d'un tel système.

# **TABLE OF CONTENT**

| DEDICATIONiii                                                           |

|-------------------------------------------------------------------------|

| ACKNOWLEDGMENTSiv                                                       |

| ABSTRACTvi                                                              |

| RÉSUMÉvii                                                               |

| CONDENSÉ EN FRANÇAISviii                                                |

| TABLE OF CONTENT xxiii                                                  |

| LIST OF TABLESxxvi                                                      |

| LIST OF FIGURESxxvii                                                    |

| ABREVIATIONSxxx                                                         |

| LIST OF ANNEXESxxxi                                                     |

| INTRODUCTION                                                            |

| 1. Heterogeneous Systems – Existing Context                             |

| 2. Heterogeneous Systems - Problematic                                  |

| 3. Objectives and Contributions                                         |

| 3.1 The Analysis of Continuous and Discrete Execution Models and        |

| Synchronization Models                                                  |

| 3.2 The Definition of a Generic Methodology for the Efficient Design of |

| Continuous/Discrete Co-Simulation Tools                                 |

| 3.3 Application of the Methodology to the Design of a Validation Tool 6 |

| 4. Document Plan 6                                                      |

|                                                                         |

| CHAPTER 1. LITERATURE REVIEW 8                                          |

| 1.1 Simulation – Based Works                                            |

| 1.1.1 Homogeneous Approach                                              |

| 1.1.2 Heterogeneous Approach                                            |

| 1.2 Formal Representation – Based Works                                 |

| 1.3 Research Project vs. Related Work                                      | 16        |

|----------------------------------------------------------------------------|-----------|

| 1.4 Conclusion                                                             | 17        |

| CHAPTER 2. EXECUTION AND SYNCHRONIZATION MODELS                            | 19        |

| 2.1 Global Execution Model                                                 | 19        |

| 2.1.1 Discrete Execution Model                                             | 20        |

| 2.1.2 Continuous Execution Model                                           | 22        |

| 2.2 Continuous/Discrete Synchronization Models                             | 24        |

| 2.2.1 Continuous/Discrete Canonical Synchronization Model                  | 25        |

| 2.2.2 Continuous/discrete rollback-based synchronization model             | 27        |

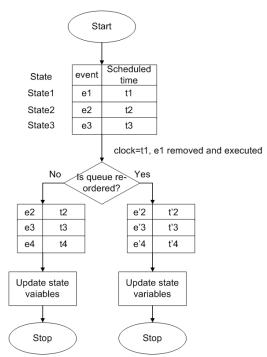

| 2.3 Events Update Schema                                                   | 29        |

| 2.3.1 The Event Update Schema for the Canonical Discrete Simulator         | 30        |

| 2.3.2 The event update schema for the rollback-based discrete simulator    | 31        |

| 2.4 Conclusion                                                             | 34        |

| CHAPTER 3. GENERIC METHODOLOGY FOR THE DESIGN C<br>SIMULATION TOOLS        | 35        |

| 3.1 Generic Methodology                                                    |           |

| 3.1.1 Definition of the Operational Semantics for the Synchroniza          |           |

| Continuous/Discrete Global Execution Models                                |           |

| 3.1.2 Distribution of the Synchronization Functionality to the Co-Sin      |           |

| Interfaces                                                                 |           |

| 3.1.3 Formalization and Verification of the Simulation Interfaces Behavior |           |

| 3.1.4 Definition of the Internal Architecture of the Simulation Interfaces |           |

| 3.1.5 The Analysis of the Simulation Tools for the Integration in          | the Co-   |

| Simulation Framework                                                       | 41        |

| 3.1.6 The Implementation of the Library Elements Specific to I             | Different |

| Simulation Tools                                                           | 42        |

| 3.2 Using Formal Methods for Co-Simulation Tools Design                       | 43 |

|-------------------------------------------------------------------------------|----|

| 3.2.1 Basic Concepts                                                          | 43 |

| 3.2.2 Definition of the Operational Semantics for the Synchronization         | in |

| Continuous/Discrete Global Execution Models                                   | 48 |

| 3.2.3 Distribution of the Synchronization Functionality to the Co-Simulation  | on |

| Interfaces                                                                    | 53 |

| 3.2.4 Formalization and Verification of the Co-Simulation Interfaces Behavior | 62 |

| 3.2.5 Definition of the Internal Architecture of the Co-Simulation Interfaces | 73 |

| 3.2.6 The Analysis of the Simulation Tools for the Integration in the C       | o- |

| Simulation Framework                                                          | 77 |

| 3.2.7 The Implementation of the Library Elements Specific to Difference       | nt |

| Simulation Tools                                                              | 77 |

| 3.3 Conclusion                                                                | 78 |

|                                                                               |    |

| CHAPTER 4. APPLICATION AND EXPERIMENTAL RESULTS                               | 80 |

| 4.1 CODIS Framework                                                           | 80 |

| 4.2 Validation of a Continuous/Discrete System, the Glycemia Level Regulator  | 82 |

| 4.3 Implementation and Results                                                | 84 |

| 4.4 Conclusion                                                                | 86 |

|                                                                               |    |

| CONCLUSION AND PERSPECTIVES                                                   | 87 |

| REFERENCES                                                                    | 91 |

| ANNEXES                                                                       | 97 |

| PUBLICATIONS                                                                  | 30 |

# LIST OF TABLES

| Table 1. Modèles de synchronisationxi                                                                                | V |

|----------------------------------------------------------------------------------------------------------------------|---|

| Table 2.1. Continuous system vs. discrete system                                                                     | 4 |

| Table 2.2. Synchronization in continuous/discrete heterogeneous systems34                                            | 4 |

| Table 3.1. Operational semantics for the C/D canonical synchronization model5                                        | 0 |

| Table 3.2. Operational semantics for the C/D rollback-based synchronization model52                                  | 2 |

| Table 3.3. Operational semantics for the Discrete Simulation Interface (DSI) for the canonical synchronization model |   |

| Table 3.4. Operational semantics for the DSI for the rollback-based synchronization model                            |   |

| Table 3.5. Operational semantics for the Continuous Simulation Interface (CSI)62                                     | 2 |

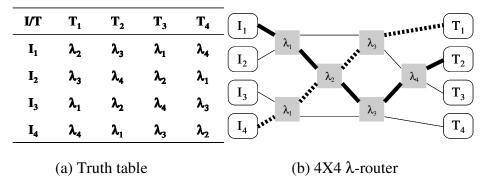

| Table 2. $4X4 \lambda$ -router truth table                                                                           | 6 |

# LIST OF FIGURES

| Figure 1. Méthodologie générique pour la conception des outils de co-simulation xvi       |

|-------------------------------------------------------------------------------------------|

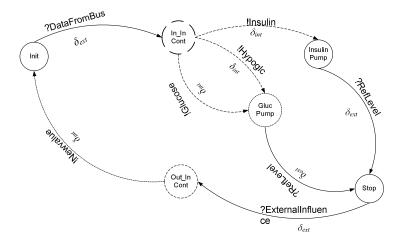

| Figure 2. Glycemia level regulator                                                        |

| Figure 3. Global co-simulation model                                                      |

| Figure 2.1. A continuous/discrete global execution model                                  |

| Figure 2.2. Event update schema in a discrete simulator ([29])                            |

| Figure 2.3. The canonical synchronization model                                           |

| Figure 2.4. The rollback-based synchronization model                                      |

| Figure 2.5. The event update schema for the canonical discrete simulator30                |

| Figure 2.6 The event update schema for the rollback-based discrete simulator32            |

| Figure 3.1 A generic methodology for co-simulation tools design                           |

| Figure 3.2. Design methodology in the flow for the automatic generation of co-            |

| simulation models                                                                         |

| Figure 3.3. The continuous/discrete system during the "Definition of the operational      |

| semantics" stage                                                                          |

| Figure 3.4. The continuous/discrete system during the "Distribution of the                |

| synchronization functionality to the co-simulation interfaces" stage38                    |

| Figure 3.5. Hierarchical representation of the generic architecture of the co-simulation  |

| model41                                                                                   |

| Figure 3.6. Example of a timed automaton                                                  |

| Figure 3.7. The global formal simulation model                                            |

| Figure 3.8. Flowchart for the discrete domain interface for the canonical synchronization |

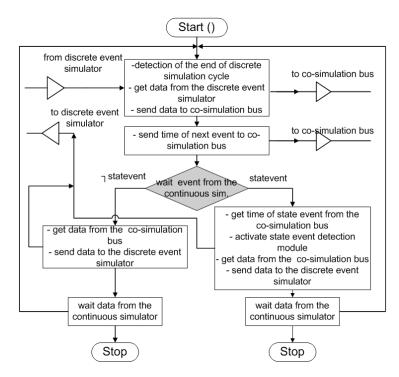

| model55                                                                                   |

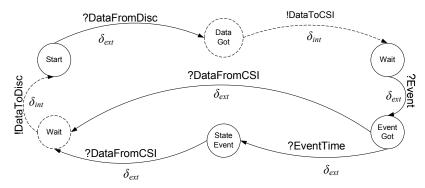

| Figure 3.9. State graph of the DSI for the canonical synchronization model represented    |

| using DEVS57                                                                              |

| Figure 3.10. Flowchart for the discrete domain interface for the rollback-based           |

|                                                                                           |

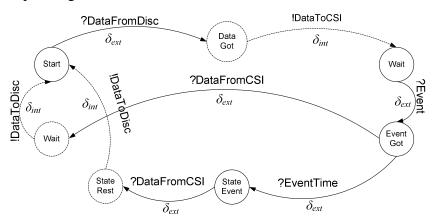

| Figure 3.11. State graph of the DSI for the rollback-based synchronization model                        |

|---------------------------------------------------------------------------------------------------------|

| represented using DEVS60                                                                                |

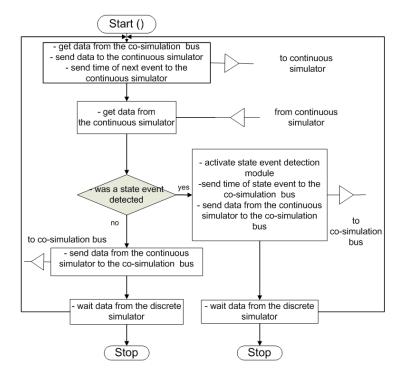

| Figure 3.12. Flowchart for the continuous domain interface                                              |

| Figure 3.13. State graph of the CSI represented using DEVS62                                            |

| Figure 3.14. The DSI for the canonical synchronization model represented as a timed                     |

| automaton63                                                                                             |

| Figure 3.15. The DSI for the rollback-based synchronization model represented as a                      |

| timed automaton65                                                                                       |

| Figure 3.16. The CSI represented as a timed automaton                                                   |

| Figure 3.17. Formal model simulation screen capture                                                     |

| Figure 3.18. The hierarchical representation of the generic architecture of the co-                     |

| simulation model with elements of the co-simulation library defined                                     |

| 73                                                                                                      |

| Figure 3.19. Internal architecture of the continuous/discrete simulation interface $\dots74$            |

| Figure 4.1. Design flow for continuous models                                                           |

| Figure 4.2. The glycemia level regulator system                                                         |

| Figure 4.3. State graph of the control sub-system represented using DEVS84                              |

| Figure 4.4. State graph of the injection sub-system represented using DEVS84                            |

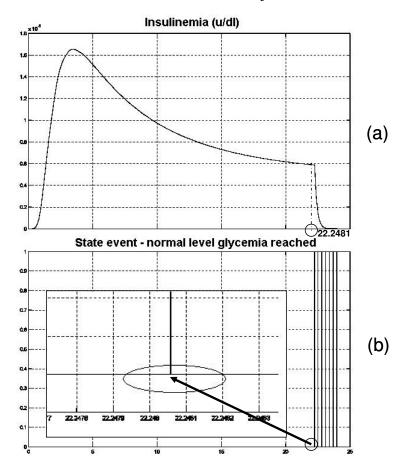

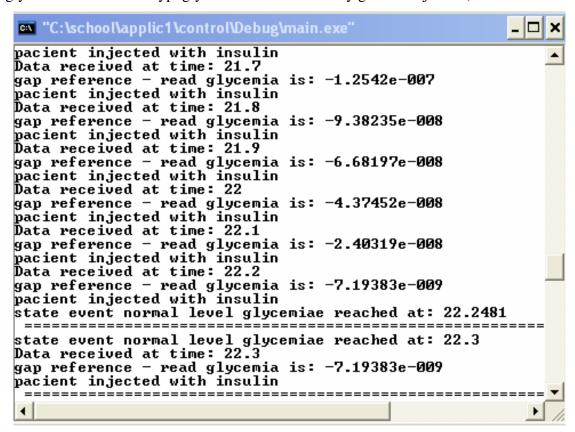

| Figure 4.5. Patient's insulinemia (a) and state event generation by CSI (b)85                           |

| Figure 4.6. State event detection by DSI                                                                |

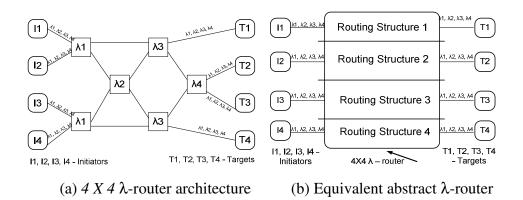

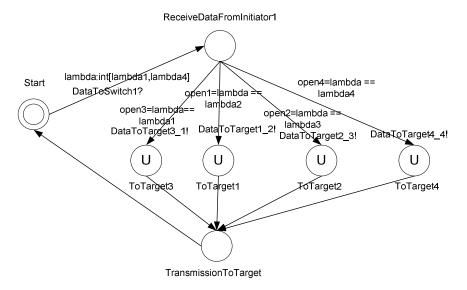

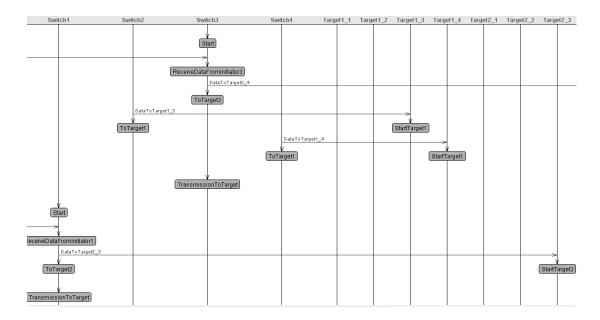

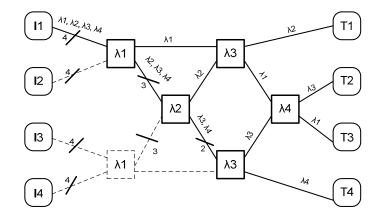

| Figure 4. ONoC overview (I=Initiator, T=Target)                                                         |

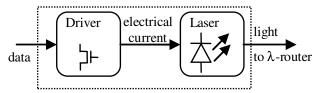

| Figure 5. Optical transmitter architecture                                                              |

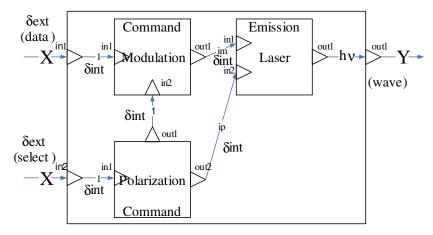

| Figure 6. Optical transmitter architecture with DEVS notations                                          |

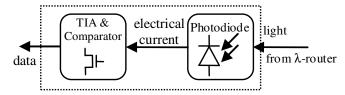

| Figure 7. Optical receiver architecture                                                                 |

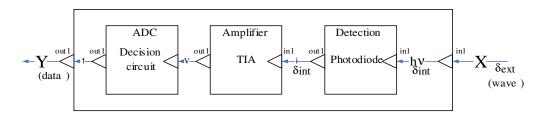

| Figure 8. Optical receiver architecture with DEVS notations                                             |

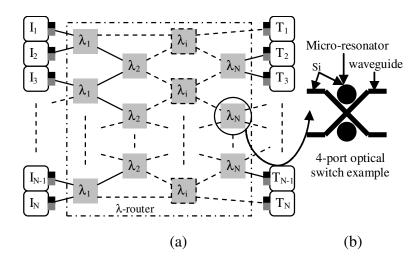

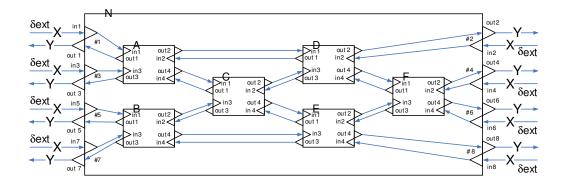

| Figure 9. $N \times N \lambda$ -router architecture (a), 4-port optical switch architecture example (b) |

|                                                                                                         |

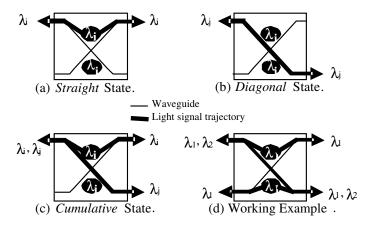

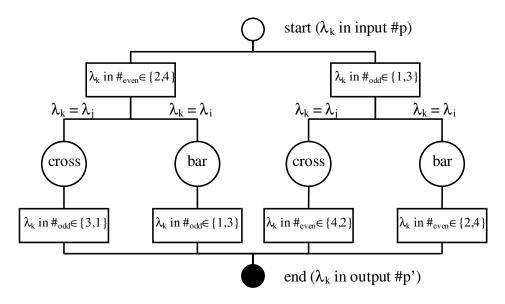

| Figure 10. Functional states of a 4-port optical switch                                                 |

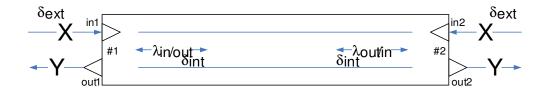

| Figure 11. Point to point bidirectional optical connection with DEVS               | . 107 |

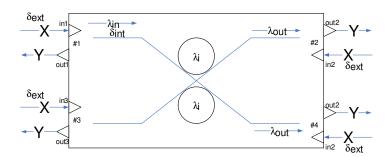

|------------------------------------------------------------------------------------|-------|

| Figure 12. Optical switch with DEVS notations                                      | 108   |

| Figure 13. State diagram of a 4-port optical switch                                | 111   |

| Figure 14. Optical switch with DEVS notations                                      | 112   |

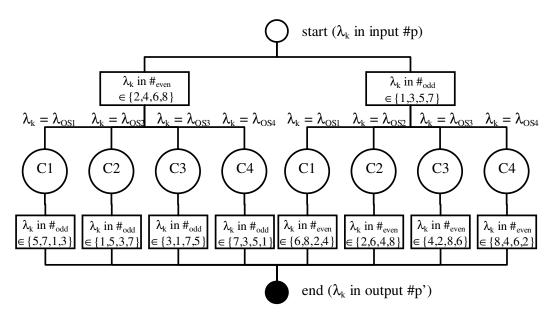

| Figure 15. State diagram of a 4 x 4 λ-router                                       | 112   |

| Figure 16. $4 \times 4 \lambda$ -router                                            | 113   |

| Figure 17. Block schema of the passive optical 4 x 4 λ-router                      | 115   |

| Figure 18. Routing structure representation                                        | 116   |

| Figure 19. λ-router simulation screen capture                                      | . 117 |

| Figure 20. Signal path in the 4 x 4 $\lambda$ -router for one initiator            | 118   |

| Figure 21. Overview of the CODIS flow                                              | . 122 |

| Figure 22. Continuous and discrete models integrating the co-simulation interfaces | 125   |

| Figure 23. Sync interface pseudo-code                                              | 127   |

| Figure 24. Sim-Inter_Out interface pseudo-code                                     | 127   |

| Figure 25. SC_inter_In interface code                                              | . 128 |

| Figure 26. SC_inter_Out interface code                                             | . 129 |

### **ABREVIATIONS**

AMS Analog mixed signal

API Application programming interface

C/D Continuous/Discrete

CDI Continuous domain interface

CMOS Complementary metal-oxide-semiconductor

CS Continuous simulator

CSP Communicating sequential processes

DDI Discrete domain interface

DEVS Discrete Event Specifications

DS Discrete simulator

FSM Finite state machine

HDL Hardware description language

IP Intellectual property

IPC Inter process communication

ISS Instruction set simulator

MoC Models of computation

MEMS Micro-electro-mechanical systems

MOEMS Micro-opto-electro-mechanical systems

MPSoC Multi-processors system on chip

ONoC Optical network on chip

SDL Specification and description language

SoC System-on-chip

SOI Silicone on insulator

VHDL VHSIC (Very High Speed Integrated Circuits) hardware description

language

# LIST OF ANNEXES

| ANNEX | 1 | COMPLEMENTARY   | RESULTS   | OPTICAL | NETWORK | ON | CHIF |

|-------|---|-----------------|-----------|---------|---------|----|------|

|       |   | MODELING AND VA | LIDATION. | •••••   | •••••   |    | 97   |

| ANNEX | 2 | CODIS FRAMEWOR  | K         |         |         |    | 122  |

#### INTRODUCTION

# 1. Heterogeneous Systems – Existing Context

System on chip (SoC) trends of the past decade observed the shrinking of the chips' size simultaneously with the growth in complexity. In response to the challenges of systems miniaturization, the International Technology Roadmap for Semiconductors (ITRS) emphasizes the More Than Moore's Law Movement that focuses on system integration rather than increasing transistor density and leads to a functional diversification in integrated systems [1]. Thus, system-on-chip are currently characterized by the heterogeneity of different modules that are particular to different application domains such as optical, electronical, mechanical, hydraulics and biological. These multi-domain systems are the main driver of the development of a wide range of products across a broad and diverse spectrum of applications in many industries, but not limited to Automotive, Aerospace, Health Care, Consumer Electronics, and others. These heterogeneous systems enable new applications and create new markets. ITRS states that heterogeneity is "a form of diversity that arises with respect to system-level SoC integration" and the design specification and validation are extremely challenging, particularly with respect to complex operating contexts [1].

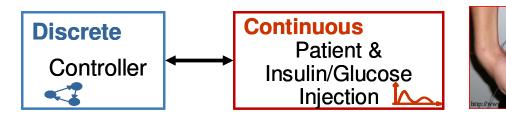

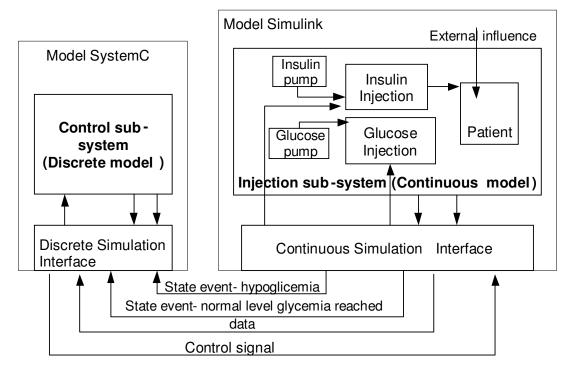

Continuous-time and discrete-event models are at the core of the design of multi-domain systems. For instance Figure 2 gives an example of a glycemia level regulator that illustrates the above mentioned aspects. The electronics domain components can be found in this application in the control block. This block controls the injection of insulin and glucose. These injections are pumps, therefore they have mechanical fluidics components. The environment is the actual patient that is injected with insulin or glucose.

Figure 2. Glycemia level regulator

The control part is generally realized in the discrete domain using simulators for hardware and/or software components (i.e VHDL [6] or SystemC [8]). The patient, the pumps and the injection process are modeled in the continuous time domain using equations (an illustrative example is the utilization of a differential equation modeling the process of insulin assimilation in the human body). For the continuous components simulators integrating equation solvers are exploited (i.e. Simulink [16]).

### 2. Heterogeneous Systems - Problematic

The integration of continuous-discrete systems implies the cooperation between different teams with different cultures, using different specification languages and simulators. Given the diversity of concepts manipulated, the global design specification and the validation are extremely challenging; their heterogeneity makes more difficult the elaboration of a global execution model for the overall validation. Such a model may be very complex.

Currently, there are two techniques used for the validation of heterogeneous systems: the formal verification and the simulation.

In order to validate a system through formal verification, its behavior needs to be represented using a formal model. This representation has to clearly define the computation and the communication (and implicitly the synchronization) for the global model and verify the behavior of the interfaces. This approach has the advantage of a rigorous and unambiguous representation of the system's behavior. This allows for the exhaustive verification of an ensemble of system's properties. The challenge is however

the system's complexity that is difficult to manage and that has impact on the time and the cost.

The validation by simulation is currently the most popular validation technique and can be defined as the execution of a global representation of a heterogeneous system. The simulation was adopted by the designers for its advantages in terms of time invested for the validation and the facility of the utilization. However the choice of simulation has an incidence on the quality of the validation – it is well known that the simulation technique does not provide an exhaustive validation.

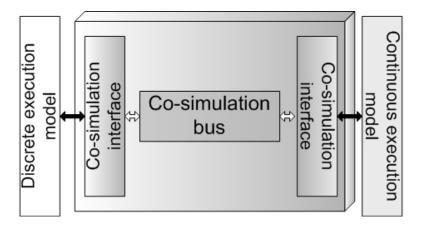

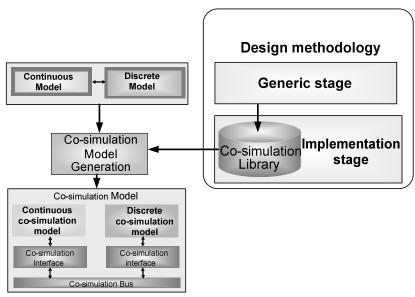

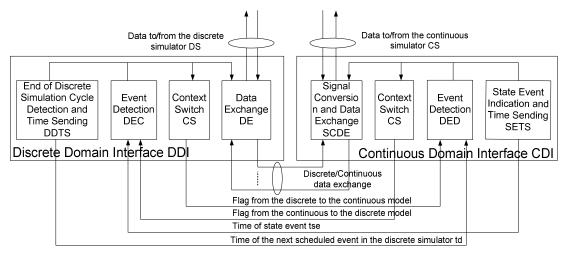

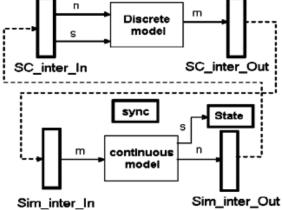

The simulation-based validation for heterogeneous systems is often referred as co-simulation. The co-simulation enables joint simulation of heterogeneous components with different execution models. Each heterogeneous component can be developed using a well known, domain-specific language and the resulting model can be reused later. The reusability advantages are: the development time, the time-to-market and the costs are reduced [3]. The co-simulation approach requires the elaboration of a global simulation model (Figure 3). The co-simulation interfaces have to provide efficient synchronization models for the adaptation of the domain specific models. This results in a complex behavior of the interfaces since their design is time consuming and a significant source of errors, they are difficult to debug and have impact on overall simulation performances. Moreover, co-simulation interfaces specification requires a deep understanding of the internal mechanism of the simulators involved in the co-simulation. Therefore, their automatic generation is very suitable.

New validation tools are required to facilitate the co-simulation during the design process. These tools generate automatically the global simulation model and consequently the co-simulation interfaces that adapt the heterogeneous models. The main role of these tools is to guarantee the correctness of the generated model, in order to accomplish this, the formal verification technique can be used during the co-simulation tools design.

Figure 3. Global co-simulation model

# 3. Objectives and Contributions

The global objective of this thesis is the definition of new solutions that reduce the time and cost of the validation stage during the design flow of heterogeneous systems. The specific objectives are:

- The definition of an approach (technique, procedure) for the design of efficient validation tools for heterogeneous systems.

- The integration in the validation stage of new aspects specific to the next generation of multi-domain heterogeneous systems: the tight interaction between the continuous and discrete models.

The main contributions of this work are:

- The analysis of the continuous and discrete execution models and the definition of global continuous/discrete (C/D) execution models based on synchronization models.

- The definition of a generic methodology for the efficient design of C/D cosimulation tools. This methodology exploits the advantages of the formal verification-based and simulation-based validation techniques.

- The application of the methodology for the design of a validation tool.

These contributions are detailed in the next three sub-sections.

# 3.1 The Analysis of Continuous and Discrete Execution Models and Synchronization Models

The execution model can be viewed as the interpretation of a model of computation. In this work, we considered the continuous/discrete heterogeneous systems and their global execution model. Discrete and continuous systems are characterized by different physical properties and modeling paradigms. A global execution model has to take into account all these paradigms. As mentioned in the previous section, the elements that compose the global model are the execution models for the different components (the continuous execution model and the discrete execution model also called in this work simulators), the co-simulation interfaces and the co-simulation bus. In this thesis, the global execution model as well as the components execution models are analyzed. Moreover, the co-simulation interfaces have to provide efficient synchronization models for the modules adaptation. The two simulators have to detect, locate and retract events that are generated by the other simulator. While the discrete events are saved in a queue and their time stamp is already known, the continuous simulator can generate events at times that are not known beforehand (named here state events). The discrete simulator must react to these events. This requirement has to be accomplished by the synchronization. This thesis discusses two synchronization models: the canonical synchronization model and the rollback-based synchronization model.

# 3.2 The Definition of a Generic Methodology for the Efficient Design of Continuous/Discrete Co-Simulation Tools

This thesis proposes a methodology for the efficient design of continuous/discrete cosimulation tools. The methodology is composed of two main stages: a generic stage and an implementation stage. In order to enable the design of co-simulation tools, the generic stage of the methodology is refined through several steps that are independent of the simulation tools used for the continuous and discrete components of the system. During these generic steps, the co-simulation interfaces are defined in a conceptual framework; their functionality and the internal structure of co-simulation interfaces are expressed using existing formalisms and temporal logic. After the rigorous definition of the required functionality for co-simulation interfaces, the designer will start the steps related to the implementation stage of the library elements using languages specific to different co-simulation tools. We emphasize here that the methodology is generic; the first stage is independent of the implementation languages of the co-simulation library.

## 3.3 Application of the Methodology to the Design of a Validation Tool

The proposed methodology was applied for the design of a co-simulation tool – CODIS (Continuous DIscrete Simulation) – that integrates the discrete simulator SystemC [8] and the continuous simulator Simulink® [16]. This tool was exploited for the validation of different heterogeneous systems such as glycemia level regulator, an analog/digital converter, a PID controller, a production chain control system and wimax system. In this thesis, we present the glycemia level regulator. Moreover, parts of the methodology were adapted for the formalization, the modeling and the validation of elements of an optical network on chip. This complementary work is presented in Annex 1.

#### 4. Document Plan

This thesis is structured in five chapters, an introduction and a final section for conclusions and perspectives. Chapter 1 presents a survey of the existing works in the continuous/discrete heterogeneous systems modeling and validation. Both, formal verification-based and simulation-based approaches will be taken into consideration. Chapter 2 presents the basic concepts concerning the global execution model of continuous/discrete heterogeneous systems, their synchronization models and events update schema for the synchronization models. Chapter 3 introduces the methodology for the generation of global execution models. This chapter includes the validation of a

synchronization models with rollback (called here the rollback-based model) and without rollback (called here the canonical model). Chapter 4 shows the application of the methodology and the results of the implementation of a glycemia regulator where the continuous model was implemented in Simulink® and the discrete model was implemented in SystemC. Finally, the last section gives the conclusions. A part of the proposed methodology was applied for a passive optical network on chip and its implementation results are given in Annex 1 as complementary results.

#### **CHAPTER 1. LITERATURE REVIEW**

The existing works in the continuous/discrete systems validation field can be roughly divided into the following classes: *simulation-based* and *formal representation-based* approaches. This chapter presents a survey of the existing works and it is structured in four sections: the first section presents the simulation-based works, the second section discusses the formal representation-based works and the third compares the work proposed in this thesis with the related work. The last section gives the conclusions.

#### 1.1 Simulation – Based Works

The components that form a heterogeneous system are specific to different application domains. In a heterogeneous design environment the co-simulation requires significant test and modeling capabilities, not only for the specific technologies (continuous or discrete-only domains) but also for the technologies combination. There are two opinions regarding the co-simulation of heterogeneous systems: one that supports a homogeneous approach and the second one that supports a heterogeneous approach [5].

## 1.1.1 Homogeneous Approach

The homogeneous approach consists of the use of only one language for the global specification of the behavior of the system; hence the representation of different parts is realized in one simulation language. The language has to have a rich and consistent semantics in order to support the heterogeneity of a complex system. The main challenge of this approach is the difficulty to find such languages and this leads to the development of new languages and this is costly in terms of training time and development of new libraries time. One can observe two strategies (techniques):

- The extension of existing tools and languages. Most of the tools created using this approach started from classical HDLs (i.e. VHDL ([6]), Verilog ([7])) to which new concepts specific to other domains such as Analog Mixed Signal

- (AMS) are added (i.e. the IEEE standards VHDL-AMS ([9], [10], [11]) and Verilog-AMS ([12], [13]).)

- The addition of an executable extension to a language that exists already (i.e SystemC ([14], [15]) that is an extension of C++).

VHDL-AMS is an extension of VHDL that can be used for modeling and validation of continuous/discrete systems. The modeling can be realized according to few categories of models: functional, behavioral, structural and physical. The VHDL scheduler was modified in order to take into account the analog solver. The developers added new objects and types and also new attributes for signals. VHDL-AMS is useful for the design of analog/digital systems but it is not powerful enough for higher levels of abstraction. [9] presents a behavioral model realized with VHDL-AMS. The authors add new concepts such as data types, analog and digital, functionality in continuous time, functionality controlled by events as well as analog-digital interactions.

Verilog-AMS ([13]) allows the designers to create and use modules that can encapsulate behavioral descriptions at high levels of abstraction as well as structural description of systems and components.

SystemC-AMS ([14]) is an extension of SystemC that was developed for continuous time systems modeling and simulation. Between other requirements, it has to provide a way to manage the interactions between the different models of computation and to support existing continuous time simulators. Therefore, the developers have to implement a library of components and solvers able to solve differential and algebraic equations. However, even if SystemC is a viable option for high level modeling and its AMS extension will improve its capabilities to provide a global co-simulation model for a continuous/discrete heterogeneous system, it is difficult to make it more powerful than the existing tools for analog simulation such as Matlab - Simulink® ([16]), mostly on the simulation precision level, availability of libraries. The examples provided in [15] are limited to the communication and signal treatment domains where the time advancement is realized with fix steps. However, this is not the case with other fields

like mechanical, electrical, micro-electro-mechanical systems (MEMS) or optical micro-systems where solvers with a variable step are required. This approach is interesting because it gives the possibility to use a synchronization mechanism for other systems' integration and a solver for complex systems and for levels of abstraction that are not normally covered by SystemC-AMS [15].

In [17] Patel and Shukla propose the extension of the modeling and simulation framework of SystemC by adding a number of cores specific for different models of computation: Syncronous Data Flow (SDF), Communicating Sequential Processes (CSP) and Finite State Machine (FSM). The simulation core of SystemC is implemented mostly for Discrete Event (DE) semantics. The cores proposed by [17] can be used with the SystemC discrete events core and it allows the developers to model and simulate specific heterogeneous systems such as SDF, CSP and FSM. The authors show with few examples that when using the specific cores, SystemC precision improved and simulation efficiency increased.

In all the tools presented in this section, the extensions are usually designed from scratch and by consequence their libraries are not as strong as the well established tools for the continuous field (i.e., Simulink®).

### 1.1.2 Heterogeneous Approach

The heterogeneous approach consists of the use of different languages that are specific for different sub-systems domains, therefore, they conserve the domain specific descriptions of the modules and the models are simulated in parallel. This task can be difficult because the simulation models are different and the global co-simulation requires a model that describes the synchronization and the interconnections between the sub-systems. The advantage of this approach is that each model can be described with a specific language and this allows for the exploitation of the best performances of the existing languages.

Some of the tools that use this approach are: Ptolemy developed by University of California at Berkeley ([18]), Chatoyant developed by University of Pittsburgh ([19], [20]) and the work realized at Techniques of Informatics and Microelectronics for integrated systems Architecture Laboratory (TIMA) in France ([5], [21], [22]).

Ptolemy ([18]) is a flexible design base that the developers can use to build prototyping environments. It supports heterogeneity and provides a tool to explore different design methodologies that support different types of design and implementation technologies. The models are built with different models of computation that characterize the behavior of the different parts of the system. Ptolemy II introduces the notion of *director* that encapsulates the behavior of a model of computation. Some of the supported directors are DE, SDF for the behavior of discrete events and synchronous data flow and CT continuous time modeling. In terms of design, the models are implemented as an ensemble of components that communicate, named *actors*. The *actors* can communicate one with each other and they can execute simultaneously, the components are defined using an *actor oriented* approach. The communication is done via *channels* and the connection is through *actors*' ports. The only interaction between the *actors* is through their *channels*. Ptolemy II also supports the *hierarchical actors* notion where *actors* can contain other *actors* and that are connected by external ports.

The components can be developed to work with multiple data types. One of the types introduced here is the behavioral type. The components and the domains support interface definitions that describe not only the static structure like the traditional systems but also the dynamical behavior. HyVisual is a hybrid systems modeler built on top of Ptolemy II [23] that supports the construction of hierarchal hybrid systems for continuous-time dynamical systems and hybrid systems.

Even though Ptolemy II is an open source code and it is an extension of Java, it is a new language and using it requires learning time for the user. The different sub-systems and components need to be developed in the same environment in order to be compatible thus they do not solve the problem of IP reuse in system design. Moreover, Ptolemy is

based on formal representation, but the formal verification of the simulation models is not considered. It also lacks of consistency for analysis and verification during conception stage ([18], [24]). Moreover the execution angles (hardware) are not taken into consideration.

Chatoyant ([19], [20]) is a simulation environment that is an extension of Ptolemy environment based on an architecture design methodology at system level. The system is decomposed into component modules that are individually characterized. The information exchanged between the modules is determined by the components: optical, electrical and mechanical. The tool can realize static and dynamical end to end simulations. The static simulations analyze the mechanical tolerances, power loss and the dynamical simulations are executed to analyze the data flow with techniques like noise analysis.

One of Chatoyant applications is the modeling of optical interconnects. Its optical libraries include passive and active optical components, optical detectors and light sources. The optical signals are represented using "linear discrete events" techniques. In order to support micro-opto-electro-mechnical (MOEM) systems, Chatoyant was extended as follows:

- Introduction of modeling techniques for diffractive optics that allow the use of diffractive models in cases where the Gaussian approximations are not valid.

- Introduction of new models for micro-lenses, micro-mirrors and mechanical actuators that allow the global simulation of the system in one mixed signal frame.

- Implementation of a Monte Carlo tolerance package to determine the worst tolerance case and the mechanical stability.

The researchers from TIMA Laboratory defined a new model for the global representation of heterogeneous systems by automatic generation of co-simulation instances [21]. The heterogeneity is given by the co-existence of different modules described at different levels of abstraction, using, for the modules specification,

different languages. This concept makes possible the systems validation during different stages in the design flow. The methodology implies the generation of the simulation bus, the simulation interfaces as well as the communication interfaces at each level of abstraction [5]. The methodology also allows the description of each module in a language specific to its domain (i.e. SDL, VHDL, ISS) and at given level of abstraction. The researchers from TIMA introduced the concept of virtual architecture that is a non executable model that represents the first step of the methodology of the automatic generation of the co-simulation models. One of the basic concepts proposed is the module's wrap that represents the abstraction of the interconnects between two heterogeneous components. Each wrap has a set of two ports: internal ports that are the module's ports and external ports that are the ports that allow the connection with the communication channels. A module and its wrap form a virtual component. The different communication channels connected to a virtual port can be grouped in virtual channels. Using these concepts the systems will be represented by a virtual architecture as a set of virtual components interconnected. For the automatic generation of cosimulation models at input of the design flow we have the description of the virtual architecture of a heterogeneous system and with elements from the co-simulation library, the co-simulation instances are generated. The strategy consists of the assembly of the existing elements into a co-simulation library. The main steps of the automatic generation of co-simulation models flow are:

- The first step consists in the analysis of the virtual architecture in order to collect the in formations necessary for the following steps.

- The second step consists in the selection of the library elements from the cosimulation library and the generation of the co-simulation interfaces. The selection is done using the results of the analysis of the system's specifications.

- The third step consists of the assembly of the system's components needed for a co-simulation instance. During this stage the co-simulation interfaces and the co-simulation bus are considered (introduced) in the initial structure of the system.

With this approach the verification/validation is realized by co-simulation. The static analysis is to check function coherence and to minimize the inter-functions coupling [5]. TIMA approach is used for hardware/software co-simulation and not for continuous/discrete models.

### 1.2 Formal Representation – Based Works

Formalism-based approaches model systems using a mathematical language like sets theory or systems theory or other formalized paradigm [4]. The integration is addressed as a composition of models of computation. These approaches propose a single main formalism to represent different models and the main concern is building interfaces between different Models of Computation (MoC). These approaches bring a deep conceptual understanding of each MoC.

The works that can be included in the formal representation – based approach were done at the University of California at Berkeley [25], the Royal Institute of Technology from Stockholm [26], [27] and the University of Arizona [28], [29] and briefly presented in this section.

In [25] a formal framework for comparing different models of computation used in heterogeneous models is presented. The authors propose a formal classification framework that makes possible to compare and express the differences between them. The framework was used to compare certain features of various MoCs such as dataflow, sequential processes and concurrent sequential processes with rendezvous, Petri nets, and discrete-event systems. The intent is "to be able to compare and contrast its notions of concurrency, communication, and time with those of other models of computation" [25].

The role of the model of computation in abstracting functionalities of complex heterogeneous systems was given in [27]. A study on the use of different models of computation for the formalization of complex heterogeneous systems functionalities is presented in [26]. The author proposes a formal framework by separating the

communication and the computation aspects. The process is divided into two parts: the *core* that is in charge with the computation and the process *shell* in charge with the communication with other processes. This separation gives a better comprehension of different problems. The designers do not have to take into consideration the problems raised by process computation while they are working on other subjects such as the communication the synchronization or the concurrence. Moreover, from a practical point of view, each part can be developed separately, integrated easier and also reused for other applications. All these elements are taken into consideration for the models of computation classification from a denotational point of view: untimed models of computation, timed models of computation, and synchronous models of computation. However, the interfaces between domains were not taken into consideration.

A meta-model named Rugby [26] that can be used for elements representation in terms of *domains*, *levels of abstraction* was defined. Rugby identifies four sub-domains: *computation, communication, domain* and *time*. The domains can be represented at different abstraction levels, from physical level to more abstract system levels (i.e. the time can be represented as continuous, discrete, clock and a causality relation).