We wish to implement a band-pass filter to demodulate an AM radio station with frequency content in the range 726–734kHz (content in this range should be accepted  $\pm 1\%$ ). We need to reject frequencies below 720kHz and above 740kHz by at least 40dB. We use a DSP system with a sampling frequency of 2MHz.

Our DSP takes 1 clk cycle for addition and 5 clk cycles for multiplication (assume other operations are zero cost). This DSP is available in versions with clk speeds of: 1MHz, 2Mhz, 5Mhz, 10MHz, 20Mhz, 50Mhz, 100MHz, 200Mhz, 500Mhz, 1Ghz, 2GHz. Faster DSPs are more expensive and use up batteries faster.

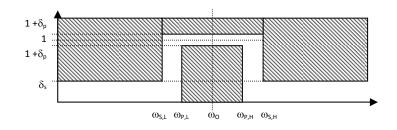

A. Sketch the filter specifications. What are  $\omega_{p,L}$ ,  $\omega_{p,H}$  and  $\omega_{s,L}$ ,  $\omega_{s,H}$ .

Answer:

$\begin{array}{l} f_{S,L} = 720 \text{kHz} \rightarrow f_{S,\text{Lnorm}} = 720 \text{kHz}/2\text{MHz} = .360 \ \text{cyc/sample} \rightarrow \omega_{S,\text{Lnorm}} = .360 \ (2\pi) \ \text{rad/sample} \\ f_{P,L} = 726 \text{kHz} \rightarrow f_{P,\text{Lnorm}} = 726 \text{kHz}/2\text{MHz} = .363 \ \text{cyc/sample} \rightarrow \omega_{P,\text{Lnorm}} = .363 \ (2\pi) \ \text{rad/sample} \\ f_{P,H} = 734 \text{kHz} \rightarrow f_{P,\text{Hnorm}} = 734 \text{kHz}/2\text{MHz} = .367 \ \text{cyc/sample} \rightarrow \omega_{P,\text{Hnorm}} = .367 \ (2\pi) \ \text{rad/sample} \\ f_{S,H} = 740 \text{kHz} \rightarrow f_{S,\text{Hnorm}} = 740 \text{kHz}/2\text{MHz} = .370 \ \text{cyc/sample} \rightarrow \omega_{S,\text{Hnorm}} = .370 \ (2\pi) \ \text{rad/sample} \\ \delta_{S} \rightarrow \text{given by 40dB spec} \ \delta_{S} = 10^{-40/20} = .01 \\ \delta_{P} \rightarrow 1\% \ \text{so} \ \delta_{P} \rightarrow 0.01 \end{array}$

### B. Calculate $\omega_c$ , $\omega_0$ for the BPF. Calculate the ideal BPF.

### Answer

$$\begin{split} & \omega_{lower cutoff} = (\omega_{S,Lnorm} + \omega_{P,Lnorm})/2 = .3615(2\pi) \text{ rad/sample} \\ & \omega_{upper cutoff} = (\omega_{P,Hnorm} + \omega_{S,Hnorm})/2 = .3685(2\pi) \text{ rad/sample} \\ & \omega_{O} = (\omega_{c,L} + \omega_{c,H})/2 = .365(2\pi) \text{ rad/sample} \\ & \omega_{c,L} = \omega_{O} - \omega_{lower cutoff} = .0035(2\pi) \\ & \omega_{c,H} = \omega_{upper cutoff} - \omega_{O} = .0035(2\pi) \\ & TBW_{L} = (\omega_{P,Lnorm} - \omega_{S,Lnorm}) = .003(2\pi) \text{ rad/sample} \rightarrow .003 \text{ cyc/sample} \\ & TBW_{H} = (\omega_{S,Hnorm} - \omega_{P,Hnorm}) = .003(2\pi) \text{ rad/sample} \rightarrow .003 \text{ cyc/sample} \\ & h_{BP,IDEAL}[n] = 2\cos[n\omega_{o}][\omega_{c}/\pi]\text{sinc}[n \omega_{c}/\pi] \quad \text{per slide } 20.17 \\ & = 2\cos[n(0.730\pi)][.007]\text{sinc}[n(.007)] \end{split}$$

Note – filter is symmetric (Transition bands have same specification)

C. Choose a windowing function and window length for this filter.

## Answer

40dB stop band specification  $\rightarrow$  Hann is acceptable window (per slide 22.14)

For Hann: 1.56/L = TBW = .003

$L = 1.56/.001 = 520 \rightarrow M = 2L+1 = 1041$

D. Calculate the expression for the FIR filter to implement this specification.

#### Answer

$h_{BP}[n] = h_{window}[n] h_{BP,IDEAL}[n]$

$= (0.5 + 0.5\cos(\pi(n-L)/L))(2\cos[(n-L)\omega_{o}][\omega_{c}/\pi]sinc[(n-L)\omega_{c}/\pi])$

$= (0.5 + 0.5\cos(\pi(n-520)/520))(2\cos[(n-520)(0.730\pi)][.007]\sin[(n-520)(.007)])$

E. To implement this filter as an FIR convolution, how many multiplies and additions are required per output sample.

# Answer:

M = 1041

| So convolution requires  |                         |

|--------------------------|-------------------------|

| M multiplies per sample  | 1041*5  clk/mult = 5205 |

| M-1 additions per sample | 1040*1  clk/add = 1040  |

|                          |                         |

Total

6245 clks/sample

F. What is the slowest clock speed DSP that can be used for this application using FIR convolution?

Answer:

2MHz sampling – Need processor > 6245\*2MHz = 12.49GHzNone of the available processors will meet the need.

- G. To implement this filter using FFT block processing, calculate how many multiplies and additions are required per output sample:

- i. for N = 2048

- ii. for *N*= 4096

## Answer:

| N=2048<br>M=1041<br>B=N-M+1 = 2                                                           | .048-1041+1 = 1008 -                                                                                                   | processing 1008 sample lengt                                                                                           | h block                                          | S                                |                                                     |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|-----------------------------------------------------|

| FFT Mults<br>FFT Adds<br>Filter Mults<br>IFFT Mults<br>IFFT Adds<br>Overlap Adds          | (N/2)(log <sub>2</sub> N-2)+1<br>Nlog <sub>2</sub> N<br>N<br>(N/2)(log <sub>2</sub> N-2)+1<br>Nlog <sub>2</sub> N<br>N | $(2048/2)(\log_2 2048-2)+1$<br>2048 $\log_2 2048$<br>2048<br>$(2048/2)(\log_2 2048-2)+1$<br>2048 $\log_2 2048$<br>2048 | 9217<br>22528<br>2048<br>9217<br>22528<br>2048   | *5<br>*1<br>*5<br>*5<br>*1<br>*1 | 46085<br>22528<br>10240<br>46085<br>22528<br>2048   |

| Total clocks per Blocks<br>Clocks / samples =149.5K/B = 149.5K/1008 = 148.3 clocks/sample |                                                                                                                        |                                                                                                                        |                                                  | 149.5K                           |                                                     |

| N=4096<br>M=1041<br>B=N-M+1 = 4096-1041+1 = 3056 - processing 3056 sample length blocks   |                                                                                                                        |                                                                                                                        |                                                  |                                  |                                                     |

| FFT Mults<br>FFT Adds<br>Filter Mults<br>IFFT Mults<br>IFFT Adds<br>Overlap Adds          | (N/2)(log <sub>2</sub> N-2)+1<br>Nlog <sub>2</sub> N<br>N<br>(N/2)(log <sub>2</sub> N-2)+1<br>Nlog <sub>2</sub> N<br>N | $(4096/2)(\log_2 4096-2)+1$<br>$4096\log_2 4096$<br>4096<br>$(4096/2)(\log_2 4096-2)+1$<br>$4096\log_2 4096$<br>4096   | 20481<br>49152<br>4096<br>20481<br>49152<br>4096 | *1<br>*5<br>*5                   | 102405<br>49152<br>20480<br>102405<br>49152<br>4096 |

| Total clocks per Blocks<br>Clocks / samples =327.7K/B = 327.7K/3056 = 107.2 clocks/sample |                                                                                                                        |                                                                                                                        |                                                  | 327.7K                           |                                                     |

H. What is the slowest clock speed DSP that can be used for this application using DSP block processing?

Answer:

| At N = $2048$ | min processor = $148.3*2$ MHz = $\sim 0.3$ GHz so use 500Mhz (1GHz more likely)      |

|---------------|--------------------------------------------------------------------------------------|

| At N = 4096   | min processor = $107.2*2$ MHz = $\sim 0.2$ GHz so use 500Mhz (likely do not need 1G) |

I. What is the processing delay for the FIR?

Answer:

N=2048 ; CPU<sub>f</sub> = 500MHz Fs = 2MHz  $\rightarrow$  Ts = 0.5x10<sup>-6</sup> secs CPU<sub>t</sub> = 2x10<sup>-9</sup> secs Processing delay

> Block delay = B\* Ts =  $1008 * 0.5 \times 10^{-6} = .504$ msec Filter delay = CLKS \* CPU<sub>t</sub> =  $149.5 \times 10^{3} * 2 \times 10^{-9} = .299$  msec

Delay = .803 msec

N=4096; CPU<sub>f</sub> = 500MHz Fs = 2MHz  $\rightarrow$  Ts = 0.5x10<sup>-6</sup> secs CPU<sub>t</sub> = 2x10<sup>-9</sup> secs Processing delay

> Block delay = B\* Ts =  $3056 * 0.5x10^{-6} = 1.528$ msec Filter delay = CLKS \* CPU<sub>t</sub> =  $327.7x10^3 * 2x10^{-9} = .655$  msec

Delay = 2.183 msec