# A High Precision Parallel Current Drive Experimental EIT System

Jeff Ashe<sup>1</sup>, David Shoudy<sup>1</sup>, Gregory Boverman<sup>1</sup>, James Sabatini<sup>1</sup>, Tzu-Jen Kao<sup>1</sup>, and Bruce Amm<sup>1</sup>

General Electric Global Research, Niskayuna, NY USA, (email: ashe@ge.com)

**Abstract:** Our parallel current drive EIT architecture can simultaneously drive 32 independent high impedance current sources and measure 32 independent precision voltage channels. Coherent modulation and demodulation is digitally implemented using field programmable gate arrays. High accuracy and precision is achieved using custom analog circuits containing modified Howland current sources coupled to negative impedance converters.

## 1 Introduction

Parallel drive EIT systems afford the ability to optimize excitation patterns for maximum distinguishability vs. conventional systems employing pairwise excitations [1]. To realize the benefits of parallel drive, it is important for the design of each channel to remain stable while achieving high output impedance. The Howland current source topology, by itself, can produce either high output resistance or low output capacitance but is incapable of producing both simultaneously. Generalized impedance converters have been used for compensating the output capacitance [2]. A negative impedance converter (NIC) circuit can generate a broad range of negative compensation capacitances but is often unstable when producing a high resistance. The Howland-NIC combination can produce low output capacitance (< 1 pF) while achieving high output resistance (>40 Mohms) by adaptively tuning the circuits to a resistance cancelling operating point using the droop circuit method [3]. A drawback of the Howland-NIC topology is a relatively narrow fractional bandwidth (slightly in excess of 30%) which creates a need for switched elements for octaves or decades of bandwidth.

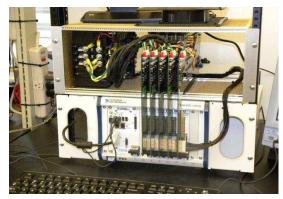

Our GENESIS parallel current drive EIT system (Figure 1) employs 32 Howland-NIC current sources connected to a FPGA-based acquisition system (PXI-7853R, National Instruments, 16 bits). The system supports excitations in excess of 20 frames per second wherein each frame can contain up to 64 orthogonal patterns. One-step reconstruction is performed in real-time on a frame by frame basis and the raw data is stored for offline analysis.

#### 2 Methods

The GENESIS system was characterized using parallel resistor-capacitor networks approximating the measured impedance of large Ag/AgCl electrodes placed on skin (nominal 1 kohm and 20 nF). After offline tuning of the Howland-NIC circuits at 10 kHz, the amplitude of each current channel was linearly increased from 0 to approximately 120 uA in 64 steps. The real and imaginary

voltages on each channel were measured after digital demodulation and matched filtering. The applied current for each channel was independently measured by returning the current through the virtual ground connection of an additional current to voltage converter. Voltage and current measurements were collected for 10,000 frames.

For analysis, the gain and phase drift of each frame was removed using a first order least squares fit vs. the measured current from the virtual ground. The residual error was computed using ohms law assuming the resistor-capacitor networks were constant and known. The maximum average residual error was determined to be less than 20 parts per million (slightly less than 16 bits accuracy) and the maximum signal to noise ratio was greater than 110 dB (slightly more than 18 bits precision).

**Figure 1: Parallel Current Drive GENESIS EIT System.** The 32 channel experimental system employs a Howland-NIC analog circuit topology with a National Instruments FPGA digital backend for modulation and demodulation.

### 3 Conclusions

The GENESIS parallel current drive experimental EIT system simultaneously provides high performance to explore optimization of simultaneous current patterns for maximum distinguishability. The Howland-NIC analog circuit designs and tuning methodologies provide performance that is consistent with the accuracy and precision of the FPGA digital modulation/demodulation implementation.

#### References

- [1] Isaacson, IEEE Trans. Med. Imag. 5:92-95, 1986

- [2] Ross et al, Phys. Meas. 24:509–516, 2003

- [3] Cook et al, IEEE Trans. Biomed. Eng. 41:713-722, 1994