### SYSC 3601, Winter 2012, Review for Final Exam

Prof. V. Aitken, Ph.D., P.Eng.

These slides are taken mostly from the lecture notes and focus on material that is important for the final exam. Additional review material, not included in this slide deck, will be presented during the remaining lectures of this term. Be there!

Students who need additional assistance to prepare for the final exam must contact me ASAP via e-mail to arrange for meeting dates/times.

# <u>History of Intel x86 μP</u>

- 4004 the first microprocessor (4-bit) 16K RAM

- 8008 (8-bit)

- 8080 (8-bit) 64K RAM, 2Mhz clock

- 8088 (8 bit)

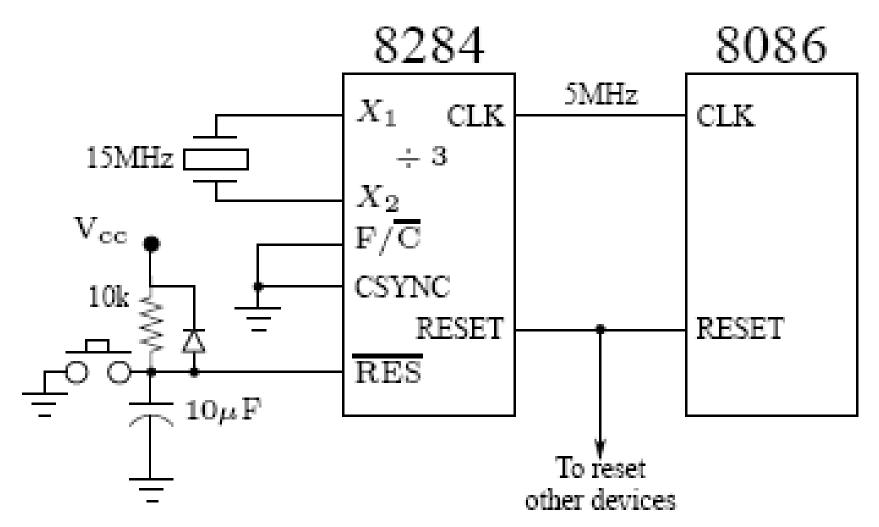

- 8086 (16-bit) 1M RAM, 5MHz clock

- 80286 (16-bit) 16M RAM, 16MHz clock

- 80386, 32-Bit, 4G RAM, 33 MHz clock

- 80486, 4G RAM, 66 MHz clock

- Pentium, 4G RAM, 66 MHz clock

- Pentium Pro, 64G RAM, 133 MHz clock

- Pentium II, 64G RAM, 233 MHz clock

- Pentium III, 64G RAM, 500 MHz clock

- Pentium 4, 64G RAM, 1.5 GHz clock

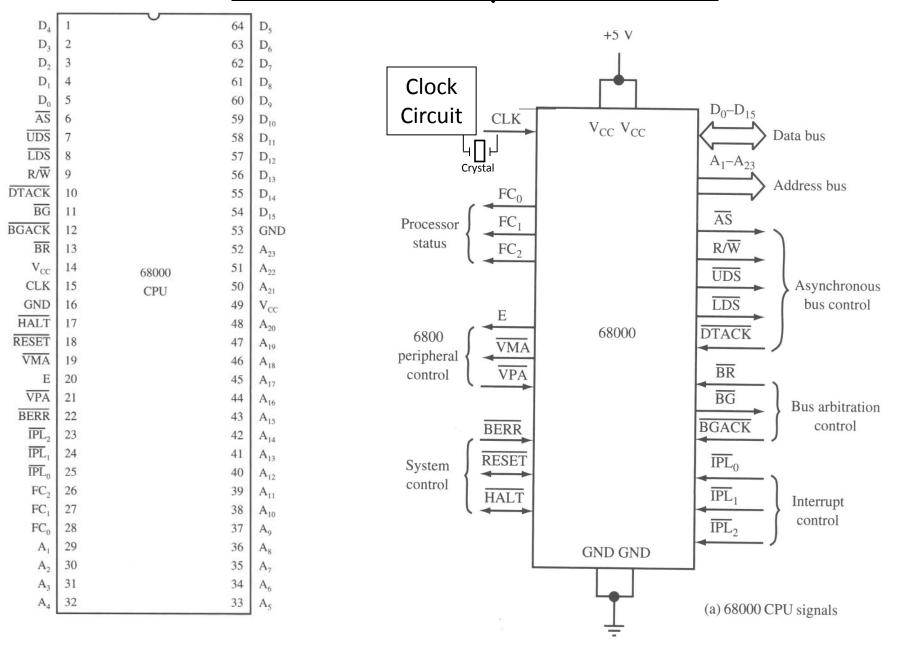

## History of Motorola 680X0 μP

- 6800 1974, 8-bit.

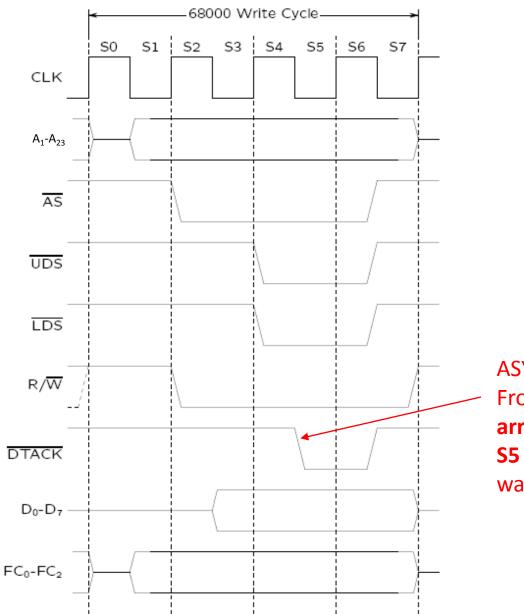

- 68000 1979, 16-bit data, 24-bit address.

- 68008 8 bit data bus, 20 bit address bus.

- 68010 1982. Added virtual memory support.

- 68020 1984. Fully 32 bit. 3 stage pipeline.

256 byte cache. More addressing modes!

- **68030** 1987. Integrated MMU into chip.

- **68040** 1991. Harvard architecture with two 4-k caches. FP on chip. 6 stage pipeline.

- **68060** 1994. Superscalar version . 10-stage pipeline. 2 integer, 1 fp unit. 8k caches.

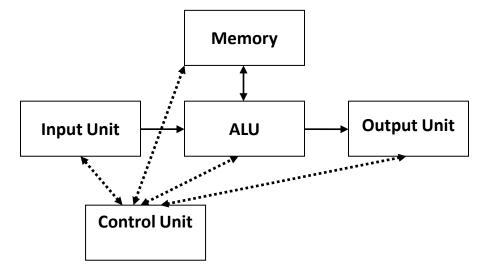

# Von Neumann Model

- Consists of **5 major components**:

- Arithmetic and Logic Unit (ALU): Performs mathematical and logical operations on its operands

- Control Unit: Produces control signals to orchestrate functioning of all other units (the boss!)

- Memory Unit: Holds both data and program (in a stored program computer)

- Input Unit: Obtains data from external sources

- Output Unit: Provides data to external sources

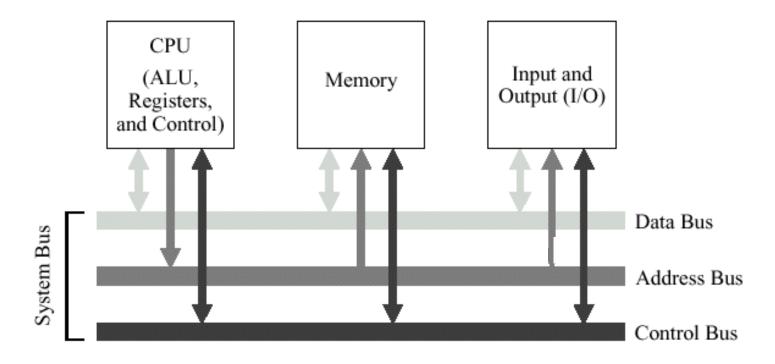

### System Bus Model1

- Refinement of the von Neumann Model

- Same 5 components, but CPU (Central Processing Unit) or microprocessor now contains both ALU and Control Unit.

- All components are attached to a shared communication pathway called the **system bus**.

### <u>Memory</u>

- Each addressable location is typically 1 byte of binary data

- Each memory element (byte) has an address, usually specified in hexadecimal notation.

- Memory size chart:

| 1KB | 2 <sup>10</sup> bytes | 1,024 bytes         |

|-----|-----------------------|---------------------|

| 1MB | 2 <sup>20</sup> bytes | 1,048,576 bytes     |

| 1GB | 2 <sup>30</sup> bytes | 1,073,741,824 bytes |

Ex: 64KB = 64 x 2<sup>10</sup> bytes = 65536 bytes 64K = 2<sup>16</sup> : need 16 address lines.

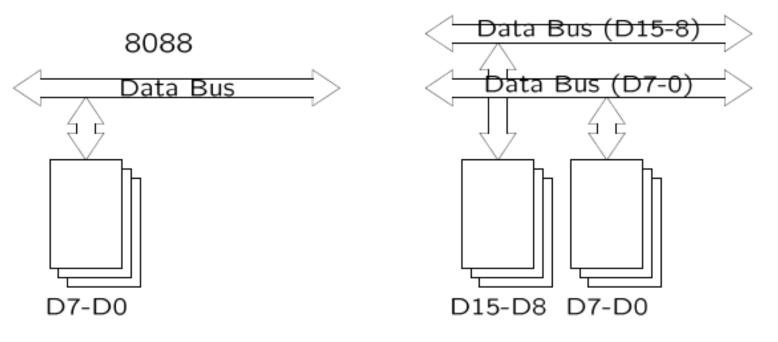

### **Memory Organization**

- Memory devices are arranged in bytes of 8-bits (modulo parity/ECC)

- µP may have 8, 16, 32, or 64 data lines...more?

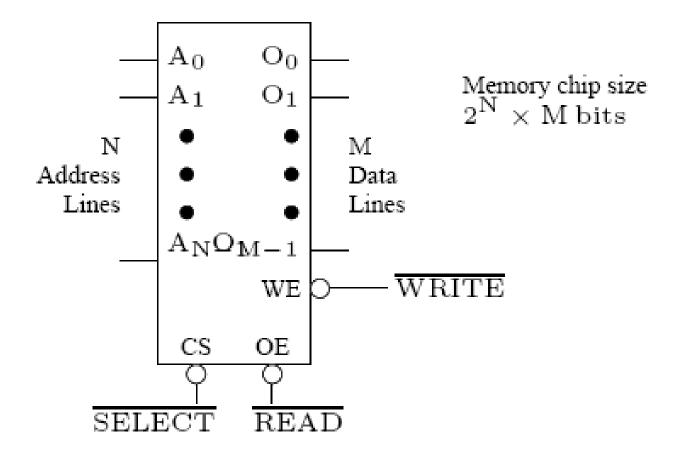

- Each memory chip returns a single byte

- Therefore, multiple banks of memory chips are used.

- Each bank requires a 'bank enable' signal

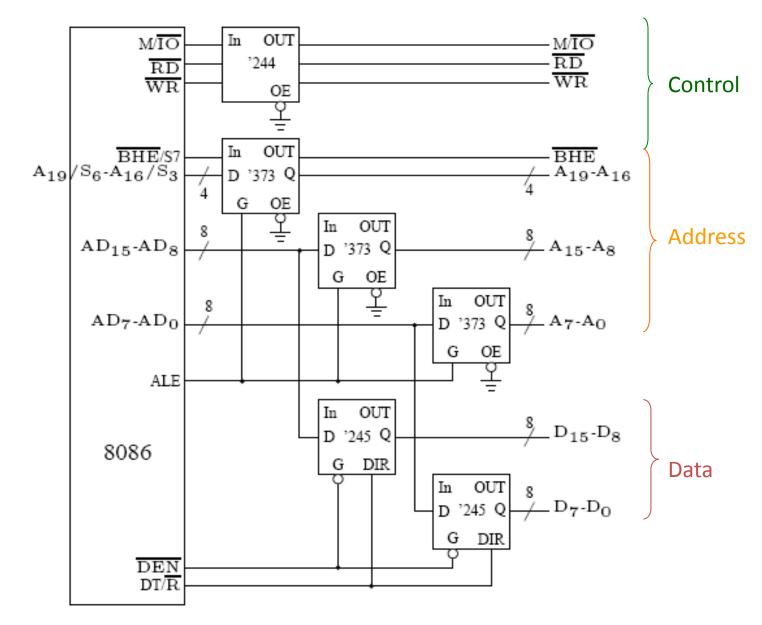

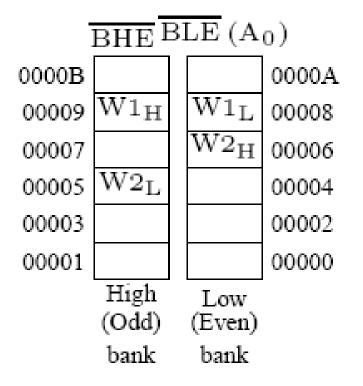

8086/186/286

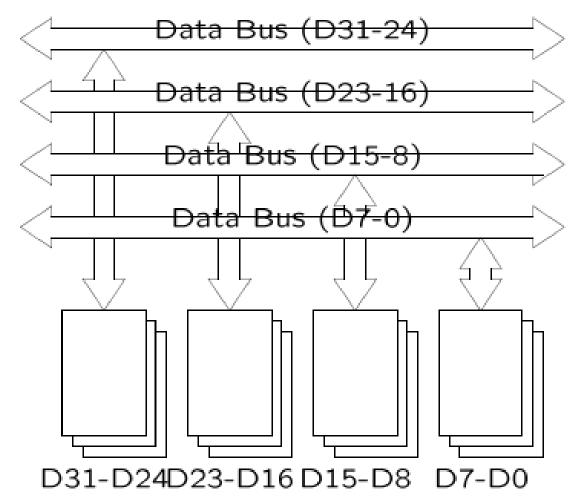

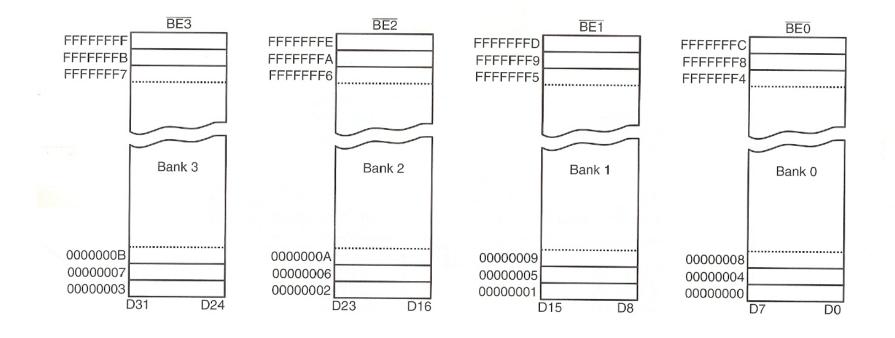

### <u>Memory Organization – 32 bit data bus</u> 80386...

- What do we do for a 64 bit data bus? 128?

- Addresses depend on Little vs Big Endien

### **32-bit Wide Memory**

- Requires 4 banks, each 8-bits wide to generate (up to) 32-bits per read/write

- Bank ID is system address 'mod 4'

- No AO, or A1 address pins (Why?)

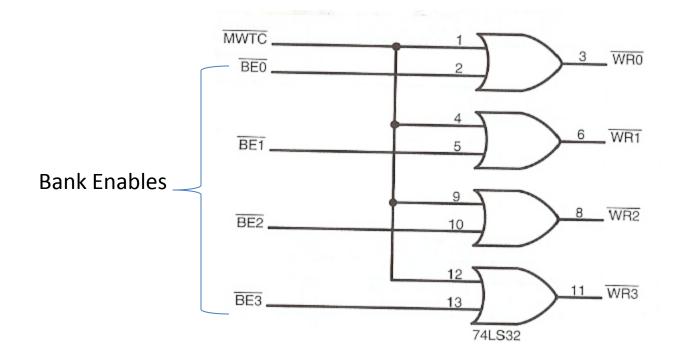

- Requires 4 bank enable signals for writes:

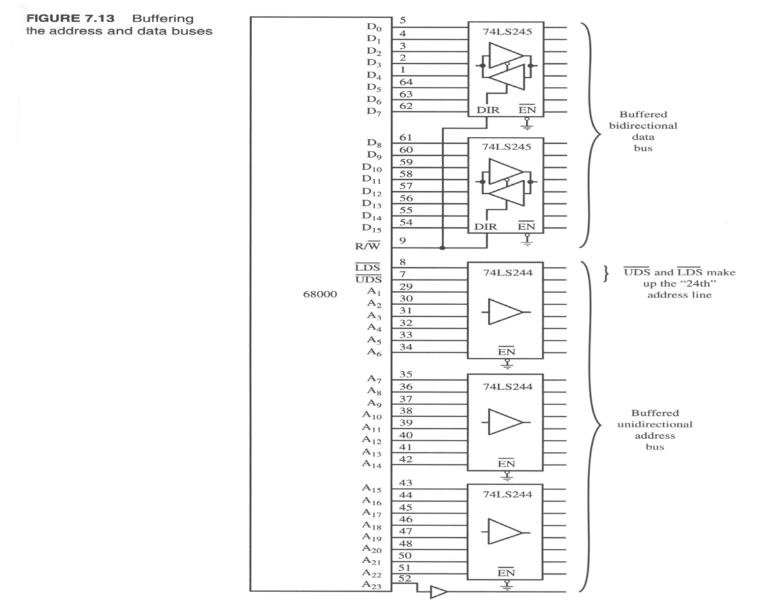

### 32-bit Data and 32-bit Address Intel Memory ('386DX)

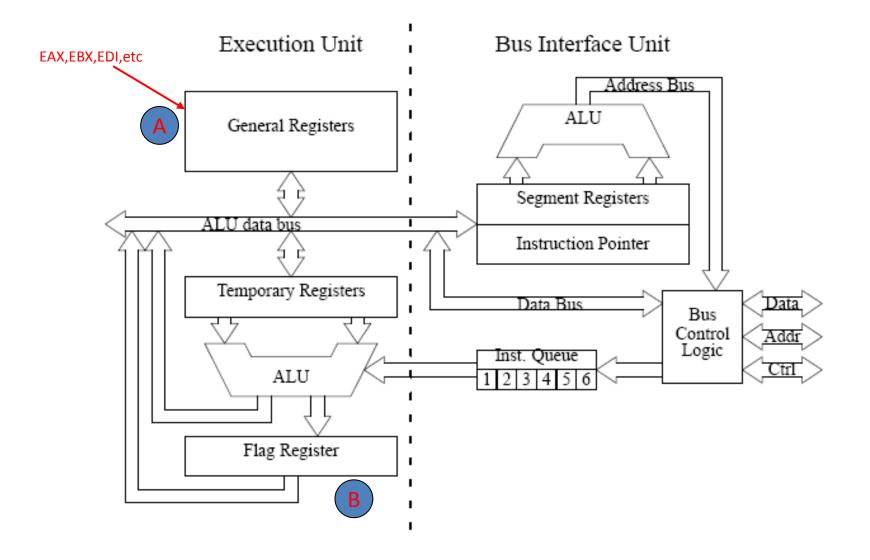

Figure 1: Internal Architecture of the 8086/88

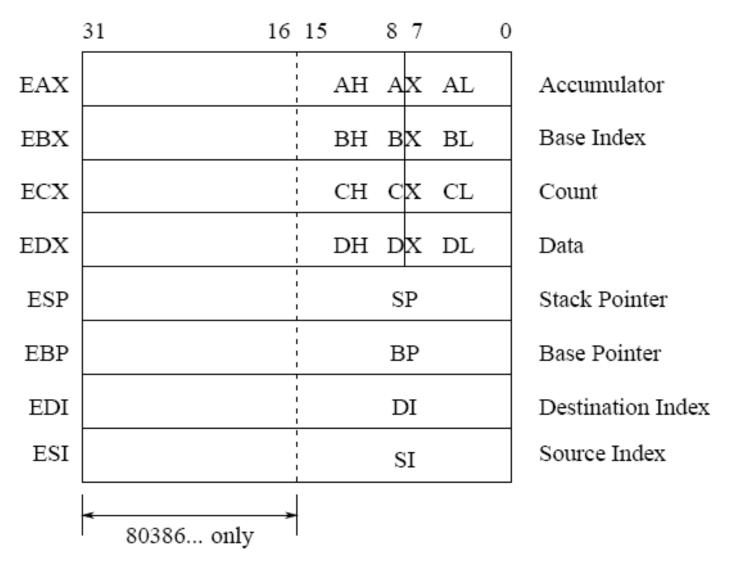

### **Intel Execution Unit – Programming Model**

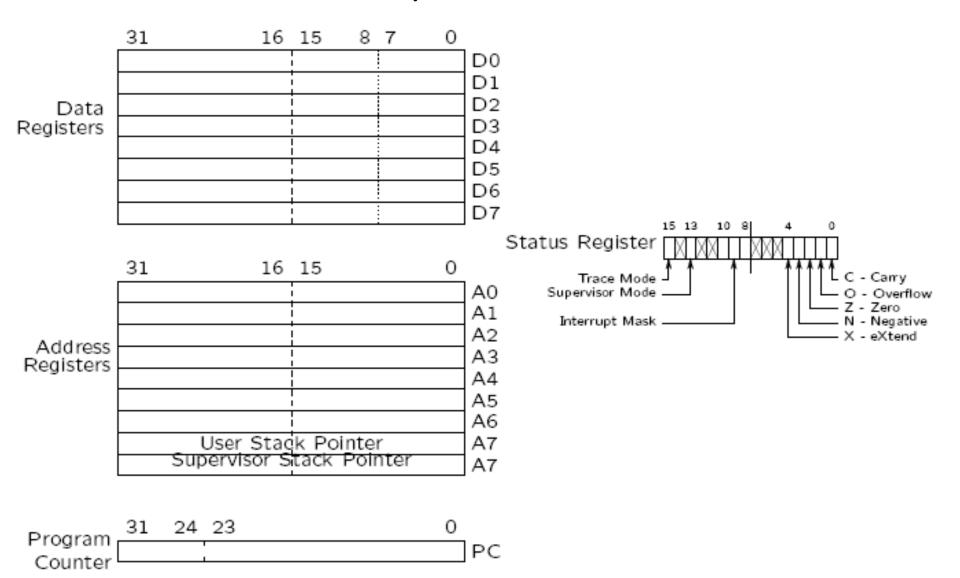

### <u>Motorola 68000 µP – Programming Model</u>

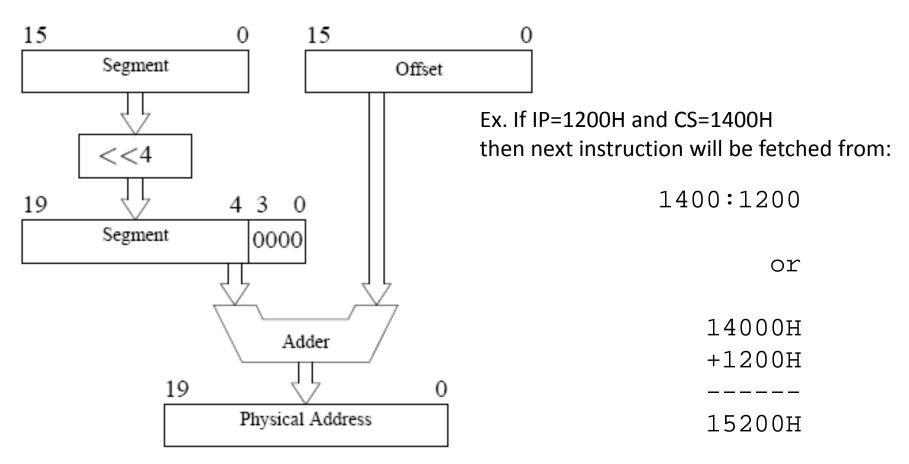

### **Intel Real Mode Address Generation**

### Not done in Motorola...use lower 24 bits of internal 32-bit address registers

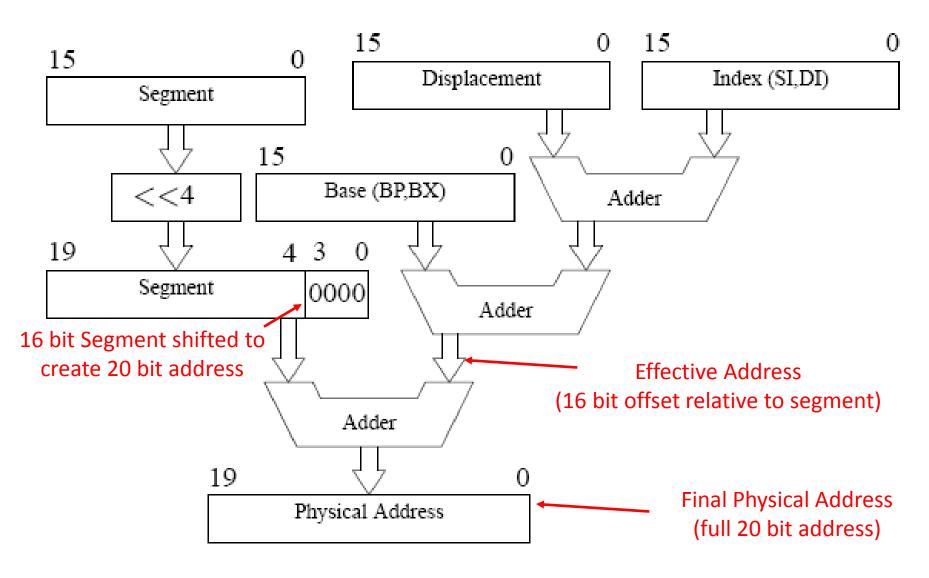

## **Intel Addressing Modes - Effective Address (EA)**

# Motorola 68000 μP – Addressing Modes There are 14 different addressing modes (more with the 68020!)

•

| Mode                           | Syntax                                                  |

|--------------------------------|---------------------------------------------------------|

| Data reg direct                | d <sub>n</sub> , n = 07                                 |

| Addr reg direct                | a <sub>n</sub> , n = 07                                 |

| Addr reg indirect              | (a <sub>n</sub> )                                       |

| with Postincrement             | (a <sub>n</sub> )+                                      |

| with Predecrement              | -(a <sub>n</sub> )                                      |

| with Displacement              | $d_{16}(a_n)$                                           |

| with Index                     | $d_8(a_n, X_m)$ (X <sub>m</sub> is any $a_m$ or $d_m$ ) |

| Relative with offset           | d <sub>16</sub> (PC)                                    |

| Relative with index and offset | d <sub>8</sub> (PC,X <sub>n</sub> )                     |

| Absolute short                 | < $\dots$ > (16-bits sign-extended to 32)               |

|                                | (for 000000-007FFF or FF8000-FFFFFF)                    |

| Absolute long                  | < > (32-bits)                                           |

| Immediate                      | #< >                                                    |

| Quick immediate                | #< > (1 byte, sign-extend to 32)                        |

| Implied                        | Register specified as part of mnemonic                  |

## <u>Motorola 68000 µP – Addressing Mode Examples</u>

• Example: A sample assembler subroutine for the 68000: Total: Find the sum of 16-bytes stored in memory.

| total | org<br>clr.w |          | ;load program counter<br>;clear D0. |

|-------|--------------|----------|-------------------------------------|

|       |              | #16,d1   | ; initialize counter                |

|       | movea.1      | #data,a0 | ;init pointer to data               |

| loop  | add.b        | (a0)+,d0 | ;add byte, increment address        |

|       | subq.b       | #1,d1    | ;decrement counter                  |

|       | bne          | loop     | ;test for zero, branch not equal.   |

|       | movea.l      | #sum,a1  | ;load address to store result       |

|       | move.w       | d0,(a1)  | ;store sum at sum                   |

|       | rts          |          | ;return from subroutine.            |

| sum   | dc.w         | 0        | ;save room for result.              |

| data  | ds.b<br>end  | 16       | ;save room for 16 data bytes.       |

- Note:

- dc.w-define a constant word, operand specifies the value to be written.

- ds.b-define storage byte, operand specifies number of bytes, but not the contents

# **Intel Assembly and Machine Language**

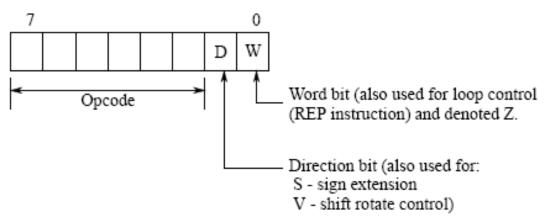

• 16 bit mode instructions take the form:

| Opcode++  | MOD-REG-R/M | Displacement | Immediate |

|-----------|-------------|--------------|-----------|

| 1-2 bytes | 0-1 byte    | 0-2 bytes    | 0-2 bytes |

- OPCODE<sup>++</sup>

- Typically 1 byte, but not always!

- Selects the operation (MOV, ADD, JMP)

|             |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ]                                               | Displacement Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-2 Dytes   |                                                                                                                                                                | 0-                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 Dyle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                               | 0-2 Dyt                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                               | 0-2 Dytes                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Direction:  |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 | "data"                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| D=0 9       | SRC=RE                                                                                                                                                         | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| D=1 1       | DST=RE                                                                                                                                                         | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Word:       |                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| W=0         | 8-Bit                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| W=1         | 16-Bit                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             |                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| "reg" Field | Bit As                                                                                                                                                         | sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ments:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 | "r/m" I                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ield B                                                           | it Assignmen                                                                                                                                                                                                                                                                                                                                                                                                                                                          | its:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 16-Bit      | 8-Bi                                                                                                                                                           | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Comment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                               | r/m                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Oper                                                             | and Address                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| (w=1)       | (w=0                                                                                                                                                           | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                 | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (BX)                                                             | + (SI) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 000 AX      | 000 2                                                                                                                                                          | AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00 ES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                               | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (BX)                                                             | + (DI) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 001 CX      | 001 (                                                                                                                                                          | CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 01 CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                               | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (BP)                                                             | + (SI) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 010 DX      | 010 1                                                                                                                                                          | DL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                               | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (BP)                                                             | + (DI) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 011 BX      | 011 1                                                                                                                                                          | BL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (5                                                               | I) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 100 SP      | 100 2                                                                                                                                                          | AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                               | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                               | à                                                                | DI) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 101 BP      | 101 (                                                                                                                                                          | CH                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (B                                                               | P) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 110 SI      | 110 1                                                                                                                                                          | DH                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (B                                                               | X) + DISP                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             | 1-2 bytes<br>Direction:<br>D=0 9<br>D=1 1<br>Word:<br>W=0<br>W=1<br>"reg" Field<br>16-Bit<br>(w=1)<br>000 AX<br>001 CX<br>010 DX<br>011 BX<br>100 SP<br>101 BP | 1-2 bytes           Direction:           D=0         SRC=RE           D=1         DST=RE           Werd:         W=0         8-Bit           W=1         16-Bit         8-Bit           'reg" Field Bit Ass         16-Bit         8-Bit           000 AX         000 0         000 0           001 CX         001 0         010 0           011 DX         010 1         101 1           100 SP         100 2         100 2           101 BP         101 0         00 2 | 1-2 bytes         0-           Direction:         D=0         SRC=REG           D=1         DST=REG           Werd:         S-Bit           W=0         S-Bit           W=1         16-Bit           "reg" Field Bit Assign           16-Bit         S-Bit           (w=1)         (w=0)           000 AX         000 AL           001 CX         001 CL           010 DX         010 DL           011 BX         011 BL           100 3P         100 AH           101 BP         101 CH | 1-2 bytes         0-1 byte           Direction: | 1-2 bytes         0-1 byte           Direction:         D=0         SRC=REG           D=1         DST=REG           Word:         W=0         8-Bit           W=1         16-Bit           "reg" Field Bit Assignments:           16-Bit         8-Bit           000 AX         000 AL         00 E3           001 CX         0010 DL         10 SS           011 DX         010 DL         10 SS           100 SP         100 AH           101 BP         101 CH | 1-2 bytes         0-1 byte         0-2 byte           Direction: | 1-2 bytes         0-1 byte         0-2 bytes           Direction:         "data           D=0         SRC=REG           D=1         DST=REG           Word:         "data           W=0         8-Bit           W=1         16-Bit           16-Bit         8-Bit           000 AX         000 AL           000 I CX         001 CL           010 DX         010 DL           010 DX         010 DL           100 SP         100 AH           101 CH         110 (BP) | 1-2 bytes         0-1 byte         0-2 bytes         0-2 bytes           Direction:         "data"         "data"           D=0         SRC=REG         "data"           D=1         DST=REG         "data"           Weod         8-Bit         "meg" Field Bit Assignments:         "r/m" Field Bit Assignment           16-Bit         8-Bit         Segment         000 (BX) + (SI) + DISP           000 AX         000 AL         00 ES         001 (BX) + (DI) + DISP           010 DX         010 DL         10 SS         010 (BP) + (SI) + DISP           011 BX         011 BL         11 DS         101 (DD) + DISP           101 SP         100 (SI) + DISP         101 (DD) + DISP         101 (DD) + DISP           101 BP         101 CH         110 (BP) + DISP         101 (BP) + DISP |  |

#### "mod" Field Bit Assignments:

111 DI 111 BH

| mod | Displacement                                                  |

|-----|---------------------------------------------------------------|

| 00  | DISP = 0*, disp-low and disp-high are absent                  |

| 01  | DISP = disp-low sign-extended to 16-bits, disp-high is absent |

| 10  | DISP = disp-high:disp-low                                     |

| 11  | r/m is treated as "reg" field                                 |

\*except if mod = 00 and r/m = 110 then EA = disp-high:disp-low

#### Effective Address Calculation Time

| EA Components        |                                  |    |  |  |  |

|----------------------|----------------------------------|----|--|--|--|

| Displacement Only    |                                  | 6  |  |  |  |

| Base or Index Only   | (BX,BP,SI,DI)                    | 5  |  |  |  |

| Disp + Base or Index | (BX,BP,SI,DI) + DISP             | 9  |  |  |  |

| Base + Index         | BP + DI, BX + SI                 | 7  |  |  |  |

| Dase + IIIdex        | BP + SI, BX + DI                 | 8  |  |  |  |

| Disp + Base + Index  | BP + DI + DISP<br>BX + SI + DISP | 11 |  |  |  |

| Dip Dux Huter        | BP + SI + DISP<br>BX + DI + DISP | 12 |  |  |  |

### MOV - MOVE (BYTE OR WORD)

| Operation | (DEST)←(SRC) |

|-----------|--------------|

|           |              |

Flags Affected None

Description MOV destination, source

MOVE transfers a byte or word from the source to the destination operand.

#### Encoding

#### Memory or Register Operand to/from Register Operand

| 1000100               | w mod reg r/m             | "data"          |

|-----------------------|---------------------------|-----------------|

| If d = 1 then SRC = 1 | A, DEST = REG, else SRC = | REG, DEST = EA. |

#### Immediate Operand to Memory or Register Operand

| 1   | 1  | 0   | 0    | 0  | 1  | 1  | W   | mod ( | ) | 0 | 0 | r/m | "data" |

|-----|----|-----|------|----|----|----|-----|-------|---|---|---|-----|--------|

| SRC | ;= | dat | a, 1 | DE | ST | =] | EA. |       |   |   |   |     |        |

#### \_\_\_\_,\_\_\_\_

| Immediate Operand to Register |        |  |  |  |  |  |

|-------------------------------|--------|--|--|--|--|--|

| 1011w reg                     | "data" |  |  |  |  |  |

| SRC = data, DEST = REG.       |        |  |  |  |  |  |

#### Memory Operand to Accumulator

| 1                                                                | 0 | 1 | 0 | 0 | 0 | 0 | W | addr-low | addr-high |

|------------------------------------------------------------------|---|---|---|---|---|---|---|----------|-----------|

| If w = 0 then SRC = addr, DEST = AL, else SRC = addr, DEST = AX. |   |   |   |   |   |   |   |          |           |

#### . .

#### Accumulator to Memory Operand

| 1    | 0                                                                | 1 | 0 | 0 | 0 | 1 | × | addr-low | addr-high |  |

|------|------------------------------------------------------------------|---|---|---|---|---|---|----------|-----------|--|

| If w | If w = 0 then SRC = AL, DEST = addr, else SRC = AX, DEST = addr. |   |   |   |   |   |   |          |           |  |

#### Memory or Register Operand to/from Segment Register

| I | 1   | 0     | 0    | 0 1   | 1     | d 0    | m        | od 0   | reg      | r/m     |           | "dat:    | 2″          |      |

|---|-----|-------|------|-------|-------|--------|----------|--------|----------|---------|-----------|----------|-------------|------|

|   | d m | ist l | be s | et su | ch ti | hat se | gment re | gister | r is enc | oded by | 2-bit reg | field. C | S cannot be | DST. |

| MOV Operands        | Clocks  | Transfers | Bytes | MOV Coding Example    |

|---------------------|---------|-----------|-------|-----------------------|

| memory, accumulator | 10      | 1         | 3     | MOV ARRAY, AL         |

| accumulator, memory | 10      | 1         | 3     | MOV AX, TEMP_RESULT   |

| register, register  | 2       | -         | 2     | MOV AX, CX            |

| register, memory    | 8 + EA  | 1         | 2-4   | MOV BP, STACK TOP     |

| memory, register    | 9 + EA  | 1         | 2-4   | MOV COUNT[DI], CX     |

| register, immediate | 4       | -         | 2-3   | MOV CL, 2             |

| memory, immediate   | 10 + EA | 1         | 3-6   | MOV MASK[BX][SI], 2CH |

| seg-reg, reg16      | 2       | -         | 2     | MOV ES, CX            |

| seg-reg, mem16      | 8 + EA  | 1         | 2-4   | MOV DS, SEGMENT_BASE  |

| reg16, seg-reg      | 2       | -         | 2     | MOV BP, SS            |

| memory, seg-reg     | 9 + EA  | 1         | 2-4   | MOV [BX] SEG_SAVE, CS |

|                                                                                                     | ION                                                                                                           |                                                        |                                                                                      |                                                                              | DEC – DECR                                                                              | EMENT                                                                                 |                                                                              |                                   |                                                                                    |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------|

| Operation                                                                                           | (DEST)+-(LSRC) + (                                                                                            | RSRC)                                                  |                                                                                      |                                                                              | Operation                                                                               | (DEST)←(DEST                                                                          | D-1                                                                          |                                   |                                                                                    |